950 Rittenhouse Rd., Norristown, PA 19403 • Tel.: 215/666-7950 • TLX 846-100 MOSTECHGY VAFG

### MCS6520 PERIPHERAL ADAPTER

### DESCRIPTION

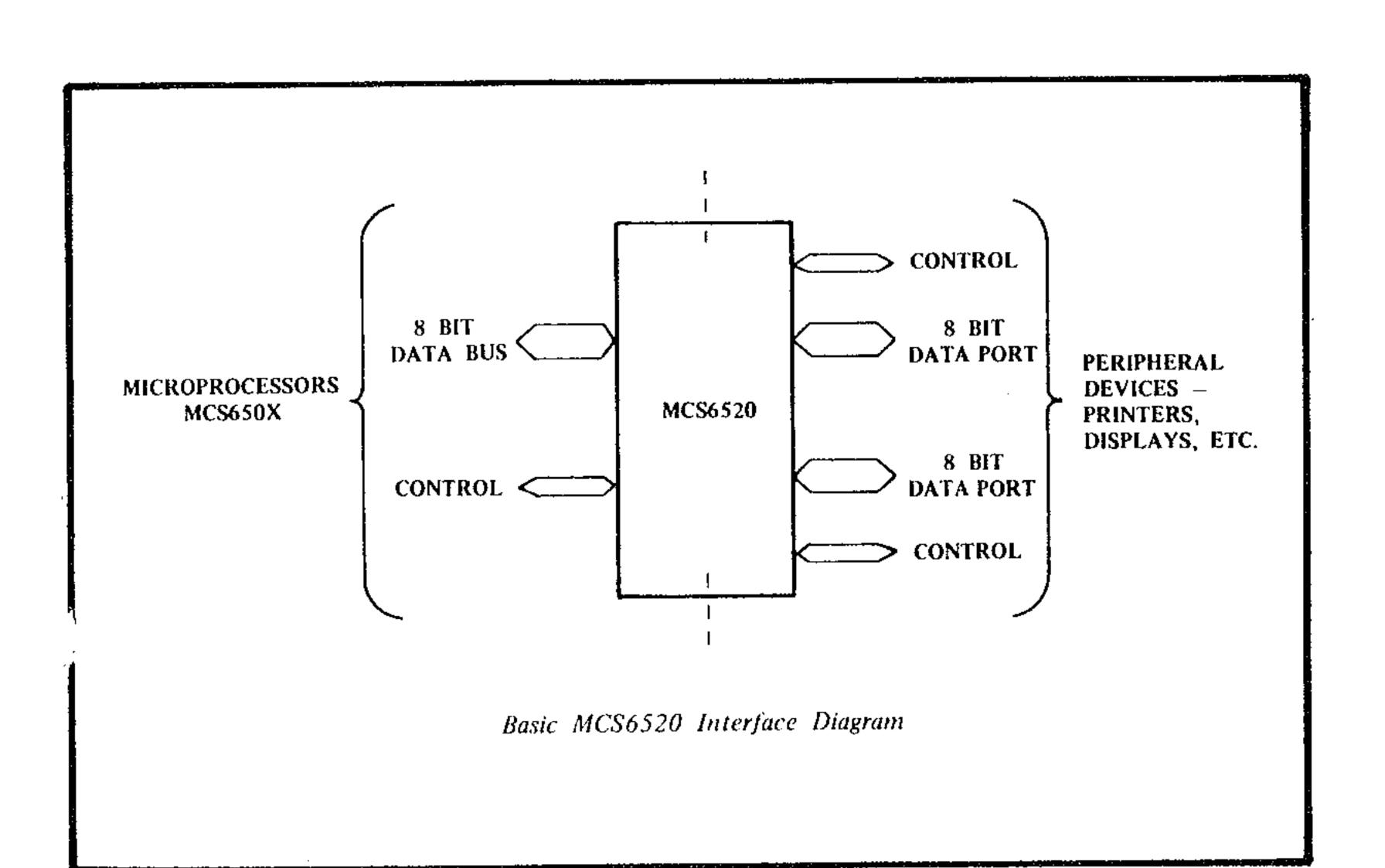

The MCS6520 Peripheral Adapter is designed to solve a broad range of peripheral control problems in the implementation of microcomputer systems. This device allows a very effective trade-off between software and hardware by providing significant capability and flexibility in a low cost chip. When coupled with the power and speed of the MCS6500 family of microprocessors, the MCS6520 allows implementation of very complex systems at a minimum overall cost.

Control of peripheral devices is handled primarily through two 8-bit bi-directional ports. Each of these lines can be programmed to act as either an input or an output. In addition, four peripheral control/interrupt input lines are provided. These lines can be used to interrupt the processor or for "hand-shaking" data between the processor and a peripheral device.

- High performance replacement for Motorola/AMI/MOSTEK/Hitachi peripheral adapter.

- N channel, depletion load technology, single +5V supply.

- · Completely Static and TTL compatible.

- · CMOS compatible peripheral control lines.

- Fully automatic "hand-shake" allows very positive control of data transfers between processor and peripheral devices.

#### MCS6520 CA1 $V_{SS}$ CA2 39 PAØ | IRQA 38 PA1 IRQB PA2 RSØ PA3 35 RS1 PA4 1 RES PA5 DØ 33 PA6 D1PA7 31 D2 10 PBØ 1 30 D3 PB1 D4 PB2 28 D5 PB3 27 D6 PB4 26 PB5 16 PB6 CS1 PB7 CS2 CB1 CSØ CB2 R/W

## SUMMARY OF MCS6520 OPERATION

See MOS TECHNOLOGY Microcomputer Hardware Manual for detailed description of MCS6520 operation.

|              |             |                                    | CA1/CBI CONTROL                                                                                  |

|--------------|-------------|------------------------------------|--------------------------------------------------------------------------------------------------|

| CRA<br>Bit 1 | (CRB) Bit 0 | Active Transition of Input Signal* | IRQA (IRQB)<br>Interrupt Outputs                                                                 |

| 0            | 0           | negative                           | Disableremain high                                                                               |

| 0            | 1           | negative                           | Enablegoes low when bit 7 in CRA (CRB) is set by active transition of signal on CA1 (CB1)        |

| 1            | 0           | positive                           | Disableremain high                                                                               |

| 1            | 1           | positive                           | Enableas explained above                                                                         |

| *Note:       |             |                                    | set to a logic 1 by an active transition of the CA1 (CB1) at of the state of Bit 0 in CRA (CRB). |

| CRA (CRB) |   |   | CA2/CB                             | 2 INPUT MODES                                                                             |  |  |

|-----------|---|---|------------------------------------|-------------------------------------------------------------------------------------------|--|--|

| Bit 5     |   |   | Active Transition of Input Signal* | IRQA (IRQB) Interrupt Output                                                              |  |  |

| 0         | 0 | 0 | negative                           | Disableremains high                                                                       |  |  |

| 0         | 0 | 1 | negative                           | Enablegoes low when bit 6 in CRA (CRB) is set by active transition of signal on CA2 (CB2) |  |  |

| 0         | 1 | 0 | positive                           | Disableremains high                                                                       |  |  |

| 0         | 1 | 1 | positive                           | Enableas explained above                                                                  |  |  |

| *Note:    |   |   | •                                  | a logic 1 by an active transition of the CA2 (CB2) the state of Bit 3 in CRA (CRB).       |  |  |

| er en | CRA |   | CA                       | 2 OUTPUT MODES                                                                                                                                                                                                                      |

|-------------------------------------------|-----|---|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 5 Bit 4 Bit 3                         |     |   | <u>Mode</u>              | Description                                                                                                                                                                                                                         |

| 1                                         | 0   | 0 | ''Handshake''<br>on Read | CA2 is set high on an active transition of the CA1 interrupt input signal and set low by a microprocessor "Read A Data" operation. This allows positive control of data transfers from the peripheral device to the microprocessor. |

| 1                                         | 0   | 1 | Pulse Output             | CA2 goes low for one cycle after a "Read A Data" operation. This pulse can be used to signal the peripheral device that data was taken.                                                                                             |

| 1                                         | 1   | 0 | Manual Output            | CA2 set low                                                                                                                                                                                                                         |

| 1                                         | 1   | 1 | Manual Output            | CA2 set high                                                                                                                                                                                                                        |

| CB2 OUTPUT MODES |       |       |       |                         |                                                                                                                                                                                                                                       |  |  |

|------------------|-------|-------|-------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                  |       | CRB   |       |                         |                                                                                                                                                                                                                                       |  |  |

|                  | Bit 5 | Bit 4 | Bit 3 | Mode                    | Description                                                                                                                                                                                                                           |  |  |

|                  | 1     | 0     | 0     | "Handshake"<br>on Write | CB2 is set low on microprocessor "Write B Data" operation and is set high by an active transition of the CB1 interrupt input signal. This allows positive control of data transfers from the microprocessor to the peripheral device. |  |  |

|                  | . 1   | 0     | 1     | Pulse Output            | CB2 goes low for one cycle after a microprocessor "Write B Data" operation. This can be used to signal the peripheral device that data is available.                                                                                  |  |  |

|                  | . 1   | 1     | 0     | Manual Output           | CB2 set low                                                                                                                                                                                                                           |  |  |

|                  | 1     | 1     | l     | Manual Output           | CB2 set high                                                                                                                                                                                                                          |  |  |

| MAXIMUM RATINGS             |          |                |          |                                                                    |

|-----------------------------|----------|----------------|----------|--------------------------------------------------------------------|

| Rating                      | Symbol   | Value          | Unit     |                                                                    |

| Supply Voltage              | $v_{CC}$ | -0.3 to +7.0   | $v_{dc}$ | This device contains circuitry to protect the inputs against       |

| Input Voltage               | Vin      | -0.3 to $+7.0$ | $v_{dc}$ | damage due to high static<br>voltages, however, it is              |

| Operating Temperature Range | $T_{A}$  | 0 to +70       | oC       | advised that normal precautions be taken to avoid application      |

| Storage Temperature Range   | Tstg     | -55 to +150    | оС       | of any voltage higher than maximum rated voltages to this circuit. |

STATIC D.C. CHARACTERISTICS ( $V_{CC}$  = 5.0 V  $\pm$  5%,  $V_{SS}$  = 0,  $T_A$  = 25°C unless otherwise noted)

| Characteristic                                                                               | Symbol          | Min                        | Тур            | Max      | Unit      |           |

|----------------------------------------------------------------------------------------------|-----------------|----------------------------|----------------|----------|-----------|-----------|

| Input High Voltage (Normal Operating Lev                                                     | VIH             | +2.0                       | _              | $v_{CC}$ | Vdc       |           |

| Input Low Voltage (Normal Operating Leve                                                     | els)            | AIF                        | -0.3           | _        | + . 8     | Vdc       |

| Input Threshold Voltage                                                                      |                 | $V_{\mathbf{I}\mathbf{T}}$ | 0.8            | _        | 2.0       | Vdc       |

| Input Leakage Current                                                                        |                 | $I_{IN}$                   |                |          |           | μAdc      |

| $V_{in} = 0$ to 5.0 $\underline{Vdc}$                                                        |                 |                            | _              | +1.0     | +2.5      |           |

| R/W, Reset, RSØ, RS1, CSØ, CS1, G                                                            | CS2,CA1,CB1,42  |                            |                |          |           |           |

| Three-State (Off State Input Current                                                         |                 | $I_{TSI}$                  |                |          |           |           |

| $(V_{in} = 0.4 \text{ to } 2.4 \text{ Vdc}, V_{CC} = \text{max}) D\emptyset$                 | -D7,PBØ-PB7,CB2 |                            | -              | +2.0     | +10       | μAdc      |

| Input High Current                                                                           |                 | $^{ m I}$ $_{ m IH}$       |                |          |           |           |

| $(V_{IH} = 2.4 \text{ Vdc})$                                                                 | Ø-PA7,CA2       |                            | -100           | -250     | -         | μAdc      |

| Input Low Current                                                                            |                 | $^{ m I}{}_{ m IL}$        |                |          |           |           |

| ` 1 <b>:</b>                                                                                 | Ø-PA7,CA2       |                            | -              | -1.0     | -1.6      | mAdc      |

| Output High Voltage                                                                          |                 | $v_{OH}$                   |                |          |           |           |

| $(V_{CC} = min, l_{Load} = -100 \mu Adc)$                                                    |                 |                            | 2.4            | **       |           | Vdc       |

| Output Low Voltage                                                                           |                 | $v_{ m OL}$                |                |          |           |           |

| $(V_{CC} = min, l_{Load} = 1.6 \text{ mAdc})$                                                |                 | J                          | _              | _        | +0.4      | Vdc       |

| Output High Current (Sourcing)                                                               |                 | $^{ m I}$ OH               |                | 1000     |           |           |

| $(V_{OH} = 2.4 \text{ Vdc})$                                                                 |                 |                            | -100           |          | -         | μAdc      |

| $(V_0 = 1.5 \text{ Vdc}, \text{ the current for drivin})$                                    |                 |                            | -1.0           | -2.5     | _         | mAdc      |

| TTL, e.g., Darlington Base) PB                                                               | Ø~PB7,CB2       | <b>T</b>                   |                |          |           |           |

| Output Low Current (Sinking)                                                                 |                 | $^{1}OL$                   | 1 (            |          |           | A J _     |

| $(V_{OL} = 0.4 \text{ Vdc})$                                                                 | OA TROD         | ¥                          | 1.6            | 1 0      | 10        | mAdc      |

|                                                                                              | QA, IRQB        | off                        | _              | 1.0      | 10        | uAdc      |

| Power Dissipation                                                                            |                 | $_{\rm PD}$                | . <del>-</del> | 200      | 500       | m₩<br>∞ E |

| Input Capacitance                                                                            |                 | $c_{in}$                   |                |          |           | pF        |

| $(V_{in} - 0, T_A = 25^{\circ}C, f = 1.0 \text{ MHz})$                                       | CAO CDO         |                            |                |          | 10        |           |

| DØ-D7, PAØ-PA7, PBØ-PB7                                                                      |                 |                            | _              | -        | 10<br>7.0 |           |

| R/W, Reset, RSØ, RS1, CSØ,                                                                   | (51,652,        |                            | _              | _        | 20        |           |

| CA1,CB1, \P2                                                                                 |                 | C                          | _              | _        | 20        |           |

| Output Capacitance<br>(V <sub>in</sub> - 0, T <sub>A</sub> = 25 <sup>O</sup> C, f = 1.0 MHz) |                 | $c_{\mathtt{out}}$         |                |          | 10        | рF        |

| (vin - 0, 1A - 25 C, 1 - 1.0 MB12)                                                           |                 |                            | <del></del>    | _        | 10        | 171       |

NOTE: Negative sign indicates outward current flow, positive indicates inward flow.

# A.C. CHARACTERISTICS

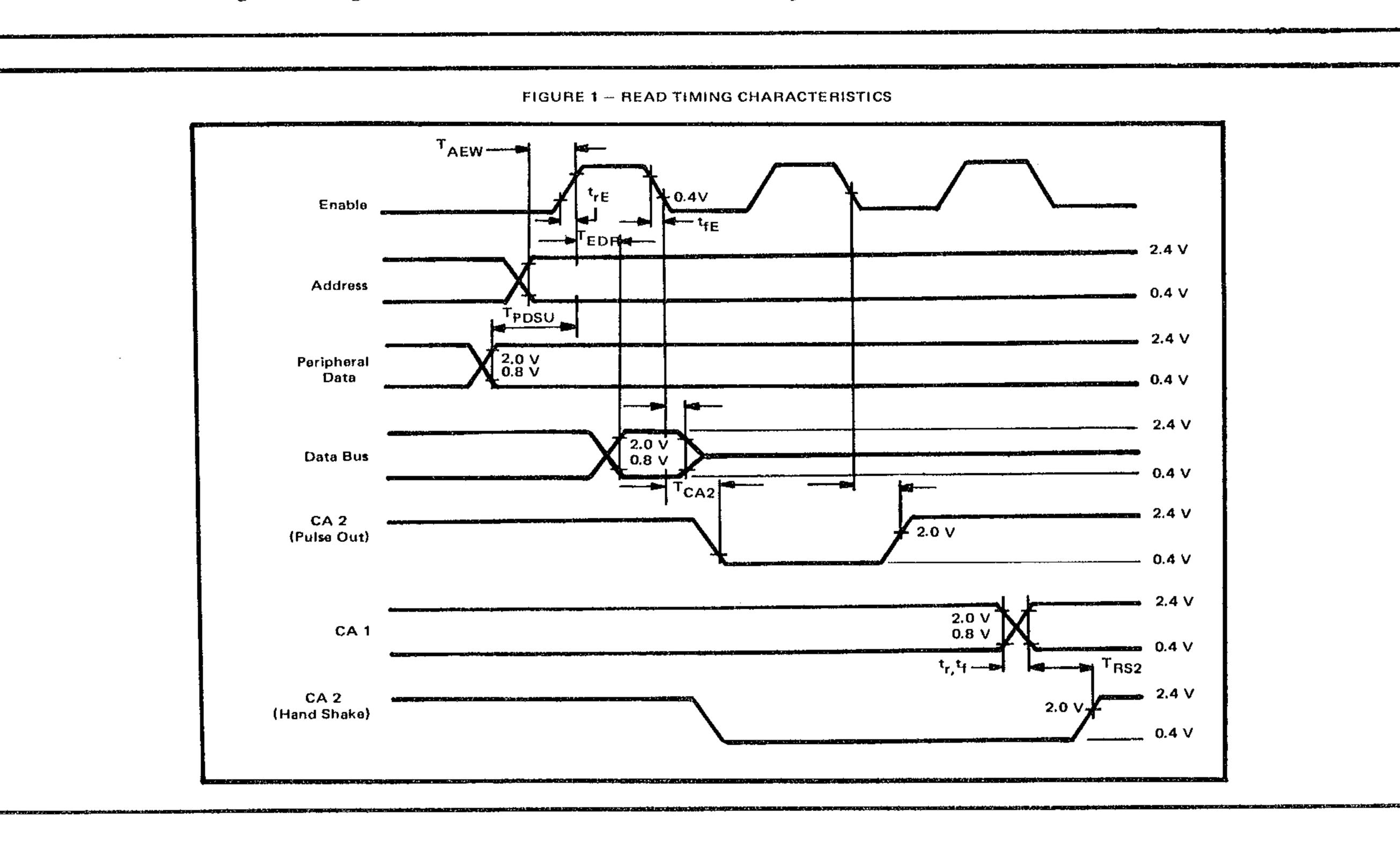

Read Timing Characteristics (Figure 1, Loading 130 pF and one TTL load)

| Characteristics                                                   | Symbo1                         | Min   | Тур         | Max | Unit           |

|-------------------------------------------------------------------|--------------------------------|-------|-------------|-----|----------------|

| Delay Time, Address valid to Enable positive transition           | TAEW                           | 180   |             | -   | ns             |

| Delay Time, Enable positive transition to Data valid on bus       | $T_{ m EDR}$                   | -     | _           | 395 | ns             |

| Peripheral Data Setup Time                                        | TPDSU                          | 300   | <b>-</b>    | -   | ns             |

| Data Bus Hold Time                                                | $T_{HR}$                       | 10    | <b>-</b>    | -   | ns             |

| Delay Time, Enable negative transition to CA2 negative transition | $T_{CA2}$                      | -     | -           | 1.0 | us             |

| Delay Time, Enable negative transition to CA2 positive transition | $T_{RS1}$                      | -     | -           | 1.0 | us             |

| Rise and Fall Time for CAl and CA2 input signals                  | $t_r, t_f$                     | -     |             | 1.0 | us             |

| Delay Time from CAl active transition to CA2 positive transition  | $T_{RS2}$                      | -     | <b>~</b>    | 2.0 | us             |

| Rise and Fall Time for Enable input                               | trE, tfE                       | -     |             | 25  | us             |

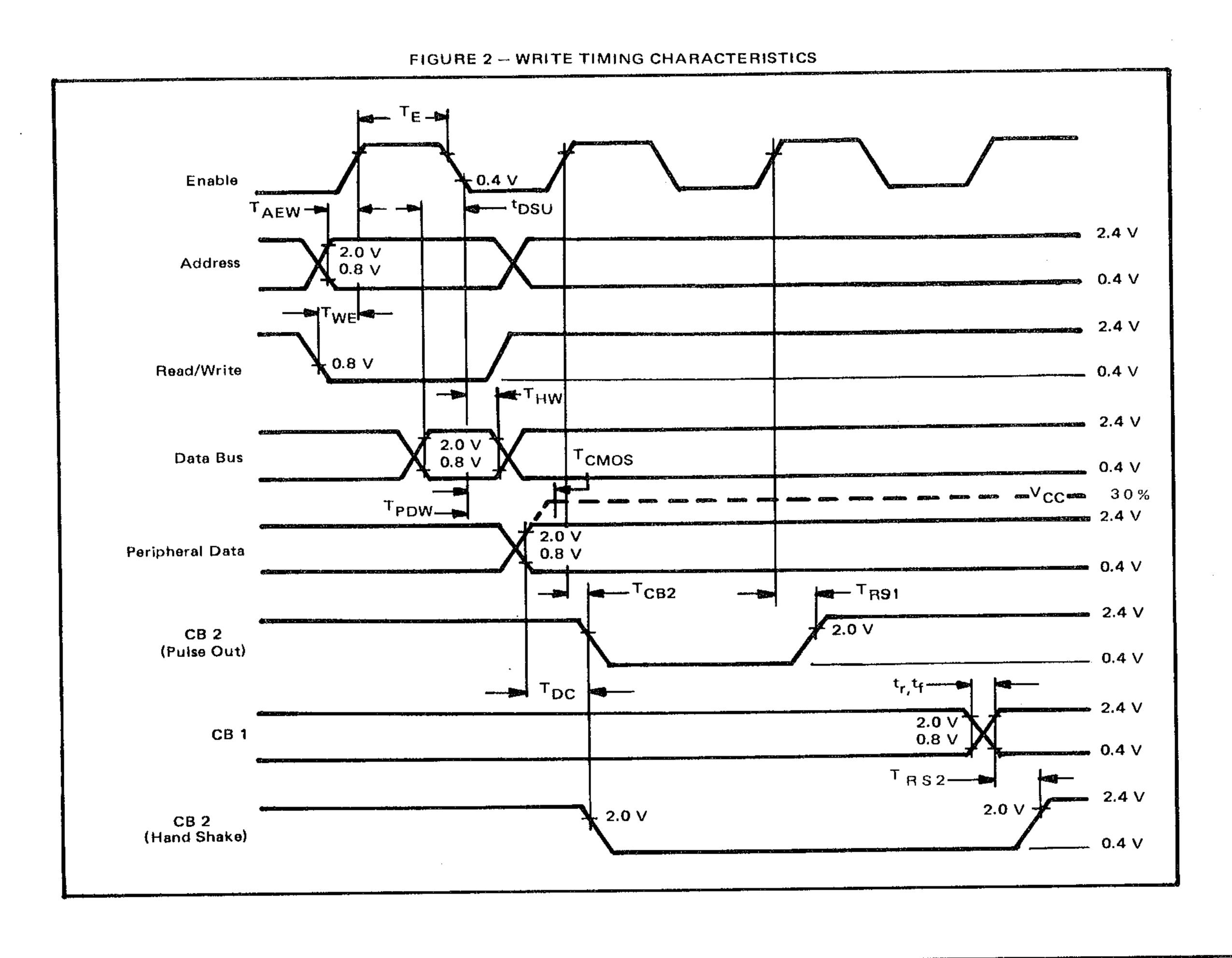

| Write Timing Characteristics (Figure 2)                           | ~ 1 1                          |       | <b>(T)</b>  | 14  | 11 <b>-</b> 4- |

| Characteristics                                                   | Symbol                         | Min   | Тур         | мах | Unit           |

| Enable Pulse Width                                                | TE                             | 0.470 | -           | 25  | μs             |

| Delay Time, Address valid to Enable positive transition           | TAEW                           | 180   | <del></del> | -   | ns             |

| Delay Time, Data valid to Enable negative transition              | $T_{DSU}$                      | 300   | -           |     | ns             |

| Delay Time, Read/Write negative transition to Enable positive     | TWE                            | 130   |             | -   | ns             |

| transition                                                        |                                |       |             |     |                |

| Data Bus Hold Time                                                | $\mathrm{T}_{HW}$              | 10    | -           |     | ns             |

| Delay Time, Enable negative transition to Peripheral Data valid   | $\mathtt{TPDW}$                | -     |             | 1.0 | μS             |

| Delay Time, Enable negative transition to Peripheral Data Valid,  | $T_{CMOS}$                     |       |             | 2.0 | μs             |

| CMOS $(V_{CC} - 30\%)$ PAØ-PA7, CA2                               |                                |       |             | 1 0 |                |

| Delay Time, Enable positive transition to CB2 negative transition | T <sub>CB2</sub>               |       |             | 1.0 | μS             |

| Delay Time, Peripheral Data valid to CB2 negative transition      | $T_{DC}$                       |       |             | 1.5 |                |

| Delay Time, Enable positive transition to CB2 positive transition | TRS1                           |       |             | 1.0 | μS             |

| Rise and Fall Time for CB1 and CB2 input signals                  | t <sub>r</sub> ,t <sub>f</sub> |       |             | 1.0 | μS             |

| Delay Time, CB1 active transition to CB2 positive transition      | T <sub>RS2</sub>               | -     | <del></del> | 2.0 | μ\$            |