## THE 68000 MICROPROCESSOR

Hardware and Software Principles and Applications

second edition

JAMES L. ANTONAKOS

# Digitized by the Internet Archive in 2011

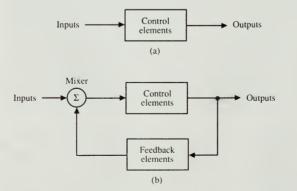

http://www.archive.org/details/68000microproces00jame

## The 68000 Microprocessor

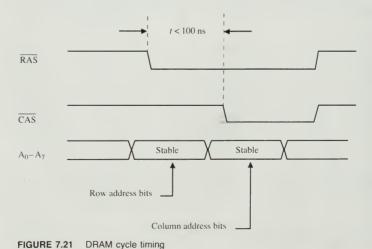

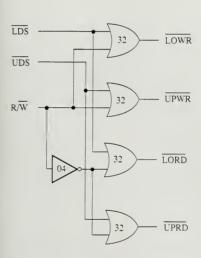

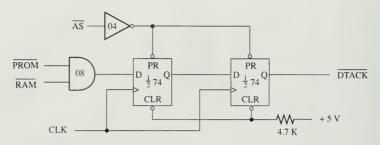

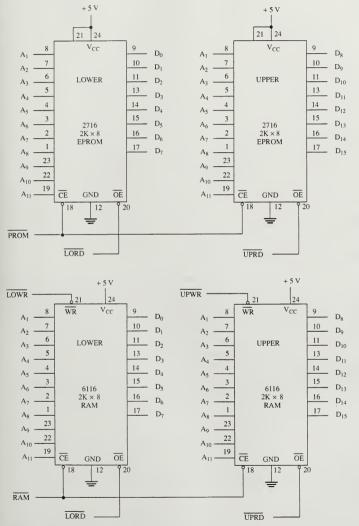

## The 68000 Microprocessor

HARDWARE AND SOFTWARE PRINCIPLES AND APPLICATIONS Second Edition

> James L. Antonakos Broome Community College

MERRILL, AN IMPRINT OF MACMILLAN PUBLISHING COMPANY New York

> MAXWELL MACMILLAN CANADA Toronto

MAXWELL MACMILLAN INTERNATIONAL New York • Oxford • Singapore • Sydney Editor: Dave Garza Production Supervisor: York Production Services Production Manager: Aliza Greenblatt Cover Designer: Proof Positive/Farrowlyne Assoc., Inc.

This book was set in Century Schoolbook by York Graphic Services, Inc., and printed and bound by R. R. Donnelley & Sons. The cover was printed by Phoenix Color Corp.

Copyright © 1993 by Macmillan Publishing Company, a division of Macmillan, Inc.

Printed in the United States of America

All rights reserved. No part of this book may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or any information storage and retrieval system, without permission in writing from the Publisher.

Earlier edition copyright © 1990 by Merrill Publishing Company.

Macmillan Publishing Company 866 Third Avenue, New York, New York 10022

Macmillan Publishing Company is part of the Maxwell Communication Group of Companies.

Maxwell Macmillan Canada, Inc. 1200 Eglinton Avenue East Suite 200 Don Mills, Ontario M3C 3N1

#### Library of Congress Cataloging-in-Publication Data

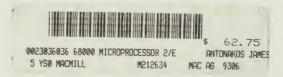

Antonakos, James L. The 68000 microprocessor : hardware and software principles and applications / James L. Antonakos. — 2nd ed. p. cm. — (Merrill's international series in electrical and electronics technology) Includes index. ISBN 0-02-303603-6 1. Motorola 68000 (Microprocessor) I. Title. II. Series. QA76.8.M6895A57 1993 004.165—dc20 92-31742 CIP

Printing: 1 2 3 4 5 6 7 Year: 3 4 5 6 7 8 9

To Alan C. Dixon, my mentor and friend, who has taught me so much

#### MERRILL'S INTERNATIONAL SERIES IN ENGINEERING TECHNOLOGY

#### INTRODUCTION TO ENGINEERING TECHNOLOGY

Pond, Introduction to Engineering Technology, 2nd Edition, 0-02-396031-0

#### ELECTRONICS TECHNOLOGY

#### **Electronics Reference**

Adamson, The Electronics Dictionary for Technicians, 0-02-300820-2

Berlin, The Illustrated Electronics Dictionary, 0-675-20451-8

Reis, Becoming an Electronics Technician: Securing Your High-Tech Future, 0-02-399231-X

#### **DC/AC Circuits**

Boylestad, DC/AC: The Basics, 0-675-20918-8

- Boylestad, Introductory Circuit Analysis, 6th Edition, 0-675-21181-6

- Ciccarelli, Circuit Modeling: Exercises and Software, 2nd Edition, 0-02-322455-X

- Floyd, Electric Circuits Fundamentals, 2nd Edition, 0-675-21408-4

Floyd, Electronics Fundamentals: Circuits, Devices, and Applications, 2nd Edition, 0-675-21310-X

Floyd, Principles of Electric Circuits, 4th Edition, 0-02-338531-6

Floyd, Principles of Electric Circuits: Electron Flow Version, 3rd Edition, 0-02-338501-4

Keown, PSpice and Circuit Analysis, 0-675-22135-8

Monssen, PSpice with Circuit Analysis, 0-675-21376-2

Tocci, Introduction to Electric Circuit Analysis, 2nd Edition, 0-675-20002-4

#### **Devices and Linear Circuits**

Berlin & Getz, Fundamentals of Operational Amplifiers and Linear Integrated Circuits, 0-675-21002-X

Berube, Electronic Devices and Circuits Using MICRO-CAP II, 0-02-309160-6

Berube, Electronic Devices and Circuits Using MICRO-CAP III, 0-02-309151-7

Bogart, Electronic Devices and Circuits, 3rd Edition, 0-02-311701-X

Tocci, Electronic Devices: Conventional Flow Version, 3rd Edition, 0-675-21150-6

- Floyd, Electronic Devices, 3rd Edition, 0-675-22170-6 Floyd, Electronic Devices. Electron Flow Version,

- 0-02-338540-5 Floyd, Fundamentals of Linear Circuits, 0-02-338481-6

Schwartz, Survey of Electronics, 3rd Edition, 0-675-20162-4

Stanley, Operational Amplifiers with Linear Integrated Circuits, 2nd Edition, 0-675-20660-X

Tocci & Oliver, Fundamentals of Electronic Devices, 4th Edition, 0-675-21259-6

#### **Digital Electronics**

Floyd, Digital Fundamentals, 4th Edition, 0-675-21217-0

McCalla, Digital Logic and Computer Design, 0-675-21170-0

Reis, Digital Electronics through Project Analysis 0-675-21141-7

Tocci, Fundamentals of Pulse and Digital Circuits, 3rd Edition 0-675-20033-4

#### Microprocessor Technology

Antonakos, The 68000 Microprocessor: Hardware and Software Principles and Applications, 2nd Edition, 0-02-303603-6

Antonakos, An Introduction to the Intel Family of Microprocessors: A Hands-On Approach Utilizing the 8088 Microprocessor, 0-675-22173-0

Brey, The Advanced Intel Microprocessors, 0-02-314245-6 Brey, The Intel Microprocessors: 8086/8088, 80186,

80286, 30386, and 80486: Architecture, Programming, and Interfacing, 2nd Edition, 0-675-21309-6

Brey, Microprocessors and Peripherals. Hardware, Software, Interfacing, and Applications, 2nd Edition, 0-675-20884-X

Gaonkar, Microprocessor Architecture, Programming, and Applications with the 8085/8080A, 2nd Edition, 0-675-20675-6

Gaonkar, The Z80 Microprocessor: Architecture, Interfacing, Programming, and Design, 2nd Edition, 0-02-340484-1

Goody, Programming and Interfacing the 8086/8088 Microprocessor: A Product-Development Laboratory Process, 0-675-21312-6

MacKenzie, The 8051 Microcontroller, 0-02-373650-X Miller, The 68000 Family of Microprocessors:

Architecture, Programming, and Applications, 2nd Edition, 0-02-381560-4

Quinn, The 6800 Microprocessor, 0-675-20515-8

Subbarao, 16/32 Bit Microprocessors: 68000/68010/68020 Software, Hardware, and Design Applications, 0-675-21119-0

#### **Electronic Communications**

Monaco, Introduction to Microwave Technology, 0-675-21030-5

Monaco, Preparing for the FCC Radio-Telephone Operator's License Examination, 0-675-21313-4

Schoenbeck, Electronic Communications: Modulation and Transmission, 2nd Edition, 0-675-21311-8

Young, Electronic Communication Techniques, 2nd Edition, 0-675-21045-3

Zanger & Zanger, Fiber Optics. Communication and Other Applications, 0-675-20944-7

#### Microcomputer Servicing

Adamson, Microcomputer Repair, 0-02-300825-3 Asser, Stigliano, & Bahrenburg, Microcomputer Servicing: Practical Systems and Troubleshooting, 2nd Edition, 0-02-304241-9

Asser, Stigliano, & Bahrenburg, Microcomputer Theory and Servicing, 2nd Edition, 0-02-304231-1

#### Programming

Adamson, Applied Pascal for Technology, 0-675-20771-1 Adamson, Structured BASIC Applied to Technology, 2nd Edition, 0-02-300827-X Adamson, Structured C for Technology, 0-675-20993-5 Adamson, Structured C for Technology (with disk), 0-675-21289-8

Nashelsky & Boylestad, BASIC Applied to Circuit Analysis, 0-675-20161-6

#### Instrumentation and Measurement

Berlin & Getz, Principles of Electronic Instrumentation and Measurement, 0-675-20449-6

Buchla & McLachlan, Applied Electronic Instrumentation and Measurement, 0-675-21162-X

Gillies, Instrumentation and Measurements for Electronic Technicians, 2nd Edition, 0-02-343051-6

#### **Transform Analysis**

Kulathinal, Transform Analysis and Electronic Networks with Applications, 0-675-20765-7

#### **Biomedical Equipment Technology**

Aston, Principles of Biomedical Instrumentation and Measurement, 0-675-20943-9

#### Mathematics

Monaco, Essential Mathematics for Electronics Technicians, 0-675-21172-7 Davis, Technical Mathematics, 0-675-2038-4 Davis, Technical Mathematics with Calculus, 0-675-20965-X

#### INDUSTRIAL ELECTRONICS/ INDUSTRIAL TECHNOLOGY

Bateson, Introduction to Control System Technology, 4th Edition, 0-02-306463-3

Fuller, Robotics: Introduction, Programming, and Projects, 0-675-21078-X

Goetsch, Industrial Safety and Health: In the Age of High Technology, 0-02-344207-7

Goetsch, Industrial Supervision: In the Age of High Technology, 0-675-22137-4

Horath, Computer Numerical Control Programming of Machines, 0-02-357201-9

Hubert, Electric Machines: Theory, Operation, Applications, Adjustment, and Control, 0-675-20765-7

Humphries, Motors and Controls, 0-675-20235-3

Hutchins, Introduction to Quality: Management, Assurance, and Control, 0-675-20896-3

Laviana, Basic Computer Numerical Control Programming, 0-675-21298-7 Reis, Electronic Project Design and Fabrication, 2nd Edition, 0-02-399230-1

Rosenblatt & Friedman, Direct and Alternating Current Machinery, 2nd Edition, 0-675-20160-8

Smith, Statistical Process Control and Quality Improvement, 0-675-21160-3

Webb, Programmable Logic Controllers: Principles and Applications, 2nd Edition, 0-02-424970-X

Webb & Greshock, Industrial Control Electronics, 2nd Edition, 0-02-424864-9

#### MECHANICAL/CIVIL TECHNOLOGY

- Keyser, Materials Science in Engineering, 4th Edition, 0-675-20401-1

- Kraut, Fluid Mechanics for Technicians, 0-675-21330-4

Mott, Applied Fluid Mechanics, 3rd Edition, 0-675-21026-7

Mott, Machine Elements in Mechanical Design, 2nd Edition, 0-675-22289-3

Rolle, Thermodynamics and Heat Power, 3rd Edition, 0-675-21016-X

Spiegel & Limbrunner, Applied Statics and Strength of Materials, 0-675-21123-9

Wolansky & Akers, Modern Hydraulics: The Basics at Work, 0-675-20987-0

Wolf, Statics and Strength of Materials: A Parallel Approach to Understanding Structures, 0-675-20622-7

#### DRAFTING TECHNOLOGY

Cooper, Introduction to VersaCAD, 0-675-21164-6

- Goetsch & Rickman, Computer-Aided Drafting with AutoCAD, 0-675-20915-3

- Kirkpatrick & Kirkpatrick, AutoCAD for Interior Design and Space Planning, 0-02-364455-9

- Kirkpatrick, The AutoCAD Book: Drawing, Modeling, and Applications, 2nd Edition, 0-675-22288-5

- Kirkpatrick, The AutoCAD Book. Drawing, Modeling, and Applications Including Version 12, 3rd Edition, 0-02-364440-0

- Lamit & Lloyd, Drafting for Electronics, 2nd Edition, 0-02-367342-7

- Lamit & Paige, Computer-Aided Design and Drafting, 0-675-20475-5

- Maruggi, Technical Graphics: Electronics Worktext, 2nd Edition, 0-675-21378-9

Maruggi, The Technology of Drafting. 0-675-20762-2 Sell, Basic Technical Drawing, 0-675-21001-1

#### **TECHNICAL WRITING**

Croft, Getting a Job: Resume Writing, Job Application Letters, and Interview Strategies, 0-675-20917-X

Panares, A Handbook of English for Technical Students, 0-675-20650-2

Pfeiffer, Proposal Writing: The Art of Friendly Persuasion, 0-675-20988-9

Pfeiffer, Technical Writing: A Practical Approach, 0-675-21221-9 Roze, Technical Communications: The Practical Craft, 0-675-20641-3

Weisman, Basic Technical Writing, 6th Edition, 0-675-21256-1

~

### PREFACE

#### INTRODUCTION

The rapid spread of microprocessors in society has both simplified and complicated our lives. Whether we rely on a computer at work or come in contact with one for other reasons, most of us have used a computer at one point or another. Most people know that a microprocessor is lurking somewhere inside the machinery, but what a microprocessor is and what it does remains a mystery.

This book is intended to help remove the mystery concerning the 68000 microprocessor through detailed coverage of its hardware and software and by means of examples of many different applications. Some of the more elaborate applications include the Apple MacIntosh computer, commercial video games and network communications controllers. Industry has also adopted the 68000 for use in digital flight control computers and other high-level applications.

The book is intended for two- or four-year electrical engineering, engineering technology, and computer science students. Professionals such as engineers and technicians would also find it a handy reference. The material is intended for a one-semester course in microprocessors.

Prior knowledge of digital electronics, including combinational and sequential logic, decoders, memories, Boolean algebra, and operations on binary numbers, is required. This presumes knowledge of standard computer-related terms, such as RAM, EPROM, TTL, and so on. Some prior experience with microprocessors is helpful but not necessary.

#### CHAPTER TOPICS

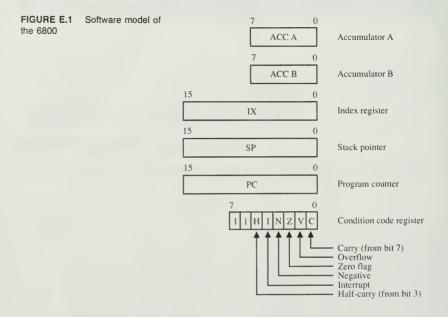

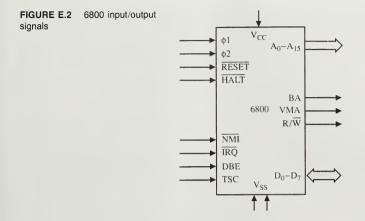

For those individuals who have no previous knowledge of microprocessors, Chapter 1, Microprocessor-Based Systems, and Appendix E, A Review of the 6800 Microprocessor, are a good introduction to the microprocessor, how it functions internally, and how it is used in a small system. Chapter 1 is a study of the overall operation of a microprocessor-based system, and includes a section on integrated circuits commonly found in such systems. Appendix E is a review—or an introduction—to the 6800 CPU, the 8-bit forerunner of the 68000. Some programming examples are included to familiarize you with the 6800.

Chapter 2, An Introduction to the 68000 Microprocessor, highlights the main features of the 68000. Data types, addressing modes, and instructions are surveyed. Also, the 68000 is compared with another processor, the 8086. Other processors in the 68000 family are examined, including the newest one, the 68030.

Chapter 3, Software Details of the 68000, provides the foundation for all programming in the remaining chapters. The 68000's instruction set and addressing modes are covered in detail, with more than 70 examples provided to help the student grasp the material. A number of simple programming applications are also presented, to lay the groundwork for additional programming in Chapters 5, 9, and 10.

Chapter 4 covers Exception Processing. The basic sequence of an exception is covered, as are multiple exceptions, prioritized exceptions, and exception handlers. This chapter may be covered after Chapter 3 and before Chapter 5, or between Chapters 5 and 9.

The first real programming efforts are found in Chapter 5, An Introduction to Programming the 68000. Numerous programming examples are included to show how the 68000 performs routine functions involving binary and BCD mathematics, string operations, data table manipulation, and control applications. Instruction timing is also covered. Each program is written in such a way that its operation may be grasped quickly. Most examples, however, leave much room for improvement. The improvements are deliberately left for the student. The end-of-chapter study questions require modifications or additions to existing routines and the creation of new ones. Chapter 5 was written in this way to challenge the student to writing his or her own code.

The hardware operation of the 68000 is covered in Chapter 6, Hardware Details of the 68000. All CPU pins are discussed, as are timing diagrams.

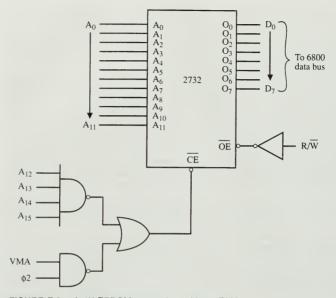

Chapter 7, Memory System Design, and Chapter 8, I/O System Design, extend the information presented in Chapter 6, and utilize it in the design of custom memory and I/O circuitry. Memory system topics include bus buffering, full- and partial-address decoding, RAM and EPROM interfacing, and Dynamic RAM. I/O System topics include memory-mapped I/O, parallel data transfer, serial data transfer, and memory-mapped video.

Advanced Programming Using 68000 Peripherals is the subject of Chapter 9. In this chapter, a number of peripherals designed for the 68000 are examined. These peripherals implement serial and parallel I/O, memory management, DMA, and floating-point operations. Programming and interfacing are discussed for each peripheral. Interfacing a non-Motorola peripheral is also covered. Other textbooks rarely pay equal attention to both hardware and software. This book was written to give equal treatment to both, culminating in a practical exercise: building and programming your own single-board computer! Chapter 10, Building a Working 68000 System, is included to give students a chance to design, build, and program their own 68000-based computer. The system contains 2K words of EPROM, 2K words of RAM, and a serial I/O device. The hardware is designed first, followed by design of the software monitor program. Some books choose to explain the operation of a commercial system, such as the MC68000 Educational Computer. This approach is certainly worthwhile, but does not give the student the added advantage of knowing *why* certain designs were used. The hardware and software designs in Chapter 10 are sprinkled with many questions, which are used to guide the design toward its final goal.

The single-board computer presented in Chapter 10 has been built by a number of senior students at Broome Community College, in an average of six weeks. It is reasonable to say that most students can build a working system in one semester.

Because of the information presented, some chapters are much longer than others. Even so, it is possible to cover certain sections of selected chapters out of sequence, or to pick and choose sections from various chapters. Chapter 3 could be covered in this way, with emphasis placed on additional addressing modes, or groups of instructions, at a rate deemed appropriate by the instructor. Also, some sections in Chapter 9 may be skipped, depending on the instructor's choice of peripheral. Some instructors may wish to cover hardware before (Chapter 6) programming (Chapters 3 and 5). There is no reason this cannot be done.

The appendixes present a full list of 68000 instructions, their allowed addressing modes, flag usage, and instruction times. In addition, they contain data sheets for three 68000-based peripherals, the 68681 Dual UART, the 68230 PI/T, and the 68881 floating-point coprocessor. This avoids the need for secondary references.

In summary, more than 175 illustrations and 35 different applications are used to give the student sufficient exposure to the 68000. The added benefit of Chapter 10, where a working system is developed, makes this book an ideal choice for a student wishing to learn about microprocessors. The old saying that 8-bit machines are easier to learn on is outdated now. The instruction sets of the newer 16-bit machines, though more complex, are easier to learn and code with. Furthermore, even though this book deals only with the 68000 family, the serious microprocessor student should be exposed to other CPUs as well. But to try to cover two or more different microprocessors in one text does not do justice to either. For this reason, attention is focused on the 68000 family and not on other CPUs.

An instructor's solutions manual is available from the publisher, containing solutions to all end-of-chapter questions. In addition, a program diskette may be ordered from the publisher upon adoption, which contains all example programs used in the text, plus source and object code files for the minimal 68000 system designed in Chapter 10. The disk allows the instructor to release programming examples to the students for studying purposes. It also allows the EPROMs required by the 68000 system to be programmed, via the supplied object code files, without having to first assemble the source.

#### CHANGES AND ADDITIONS FOR THE SECOND EDITION

A number of changes and additions were made to the text in this edition. The changes mostly involve the renumbering of several chapters, and have not removed *any* information that was present in the first edition. The old Chapter 2, A Review of the 6800 Microprocessor, has been moved to become Appendix E. The old Chapter 4, Hardware Details of the 68000, is now Chapter 6. The old Chapter 8, Memory and I/O Systems, has been split into separate chapters: Chapter 7, Memory System Design, and Chapter 8, I/O System Design. Old Chapters 3, 5, 6, and 7 have become Chapters 2 through 5. This reordering places the major software and hardware chapters into two groups (Chapters 2 through 5, and Chapters 6 through 8).

Many of the additions include *new* software examples. These examples cover sorting, binary and BCD number conversions, and stack and queue operations. In addition, a special topic called the **Calculator Project** appears in several chapters, and is included to help show how the 68000 is used in a complete system.

Many chapters now also contain additional study questions to further challenge the student.

To insure that students get the opportunity to solve the study questions on their own, the answers to selected study questions have been removed. This was done to discourage access to answers before a real attempt is made to solve the study question. All study questions are solved in the instructors solution manual.

#### ACKNOWLEDGMENTS

I would like to thank all of the students and instructors who used the first edition, and who contributed many helpful comments.

The following individuals contributed many helpful comments during the rewrite, and I am grateful for their advice:

Michael Eshaghnia, DeVry Institute of Technology, Los Angeles; Parimal A. Patel, The University of Texas at San Antonio; David Cummings, Marguerite Rawlston, Myron Sveum, Metropolitan State College, Denver; and R. Sridhar, SUNY at Buffalo.

### CONTENTS

#### CHAPTER 1 Microprocessor-Based Systems

Objectives 1

1.1 Introduction 1

1.2 System Block Diagram 2

1.3 Microprocessor Operation 6

- 1.4 Hardware/Software Requirements 6

- 1.5 Evolution of Microprocessors 8

- 1.6 Special Gates for Microcomputer Use 15

The Octal Buffer

10

The Octal Bus Transceiver

11

The Octal D-Type Flip-Flop

12

The 3- to 8-Line Decoder

13

The Priority Encoder

13

The Parity Generator/Checker

14

- 1.7 The Calculator Project 14

- 1.8 Summary 15 Study Questions 16

#### **CHAPTER 2**

#### An Introduction to the 68000 Microprocessor

Objectives 19

- 2.1 Introduction 19

- 2.2 The Software Model of the 68000 20

- 2.3 A Functional Description of the 68000 21

- 2.4 68000 Data Organization 21

- 2.5 68000 Instruction Types 22

- 2.6 68000 Addressing Modes 23

1

- 2.7 68000 Exceptions 24

- 2.8 Advantages of the 68000 25

- 2.9 The 68008: An 8-Bit Spinoff 27

- 2.10 The 68010: A Virtual-Memory Processor 27

- 2.11 The 68020: A True 32-Bit Machine 28

- 2.12 The 68030: An Enhanced 32-Bit Machine 29

- 2.13 Beginning the Calculator Project 30

- 2.14 Summary 31 Study Questions 31

#### CHAPTER 3 Software Details of the 68000

Objectives 33

- 3.1 Introduction 33

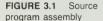

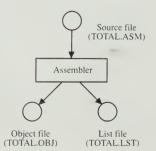

- 3.2 Assembly Language Programming 34

- 3.3 68000 Instruction Types 38

- 3.4 68000 Addressing Modes 39

Data Register Direct 39 Address Register Direct 40 Address Register Indirect 40 Address Register Indirect with Postincrement 41 Address Register Indirect with Predecrement 41 Address Register Indirect with Displacement 42 Address Register Indirect with Index 43 Absolute Short Address 44 Absolute Long Address 44 Program Counter with Displacement 44 Program Counter with Index 45 Immediate Data 47 Quick Immediate Data 47 Implied Addressing 48

3.5 The 68000's Instruction Set 48

The Condition Codes 48 The Data Transfer Group 49 The Arithmetic Group 55 The Logical Group 63 The Shift and Rotate Group 65 The Bit Manipulation Group 67 The BCD (Binary Coded Decimal) Group 69 The Program Control Group 70 The System Control Group 75

- 3.6 How an Assembler Generates Machine Code 79

- 3.7 Programming Examples 80

Data Summing 80 Searching a List 81

Block Move 81 Baise to Power 82 A Subroutine Dispatcher 82 The Calculator Control Program 83

3.8 Summary 84 Study Questions 85

#### CHAPTER 4 Exception Processing

89

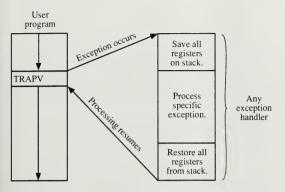

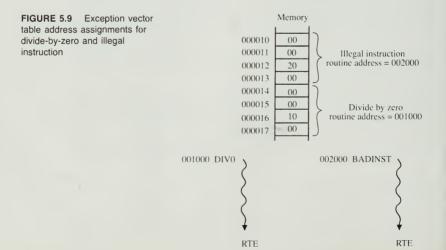

Objectives 89 Introduction 89 4.1 4.2 Execution States 90 4.3 Privilege States 90 Changing the Privilege State 4.4 94 4.5 Exception Processing 94 Exception Processing Sequence 95 Step 1: Adjust Status Register 95 Step 2: Get Vector Number 95 Step 3: Save Processor Information Step 4: Fetch New Program Counter 98 4.6 Multiple Exceptions 99 4.7 Special Exceptions 100 Reset 100 Bus Error 101 Address Error 101 Trace 101 Interrupts 102 Illegal Instructions 104 Unimplemented Instructions 106 Privilege Violation 106 TRAP 106 TRAPV 107 CHK 107 Divide-by-Zero 108 4.8 Exception Handlers 108

97

4.9 Summary 110 Study Questions 110

#### CHAPTER 5

#### An Introduction to Programming the 68000

Objectives 113

5.1 Introduction 114

5.2 Tackling a Large Programming Assignment 114 The Assignment 114

|                              | Breaking the Program Down into Modules 115                                                                                                                                                                                              |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | Testing the Modules 116<br>Creating the Final Module 116                                                                                                                                                                                |

| 5.3                          | Data Gathering 118                                                                                                                                                                                                                      |

|                              | The Keyboard Buffer 118                                                                                                                                                                                                                 |

|                              | Packing BCD Numbers 119                                                                                                                                                                                                                 |

| 5.4                          | Searching Data Tables 120                                                                                                                                                                                                               |

|                              | Searching for a Single Item 120<br>Searching for the Highest Integer 121<br>Comparing Strings 122<br>A Command Recognizer 122                                                                                                           |

| 5.5                          | Sorting 123                                                                                                                                                                                                                             |

| 5.6                          | Computational Routines 125                                                                                                                                                                                                              |

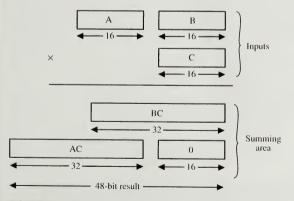

|                              | Binary Addition 125<br>Binary Subtraction 126<br>Binary Multiplication 127<br>Binary Division 128<br>BCD Addition 129<br>BCD Subtraction 130<br>BCD Multiplication 130<br>BCD Division 132<br>Deriving Other Mathematical Functions 134 |

| 5.7                          | Number Conversions 138                                                                                                                                                                                                                  |

|                              | BCD to Binary Conversion138Binary to BCD Conversion139                                                                                                                                                                                  |

| 5.8                          | Control Applications 140                                                                                                                                                                                                                |

|                              | A Computerized Burglar Alarm 141<br>A Constant-Speed Motor Controller 146                                                                                                                                                               |

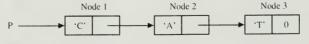

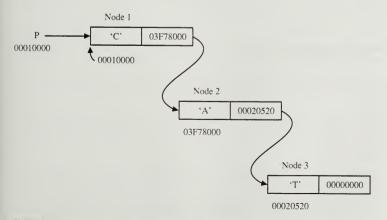

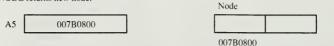

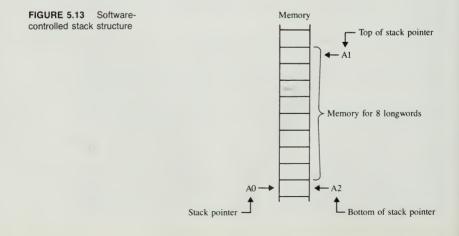

| 5.9<br>5.10<br>5.11<br>5.12  | Instruction Execution Times 147<br>Exception Handling 149<br>Linked Lists 152<br>Stacks and Queues 155                                                                                                                                  |

|                              | Stacks 155<br>Queues 156                                                                                                                                                                                                                |

| 5.13<br>5.14<br>5.15<br>5.16 | Multitasking 158<br>Memory Management 160<br>Special Calculator Functions 162<br>Summary 164<br>Study Questions 164                                                                                                                     |

#### **CHAPTER 6**

#### Hardware Details of the 68000

Objectives 169

6.1 Introduction 169

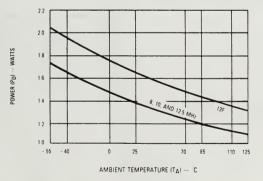

- 6.2 CPU Specifications 170

- 6.3 CPU Pin Descriptions 170

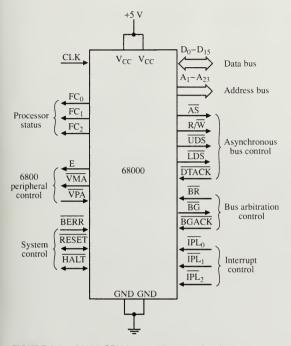

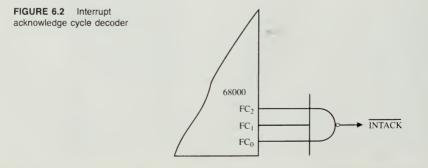

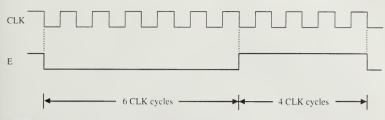

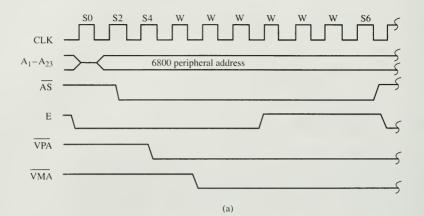

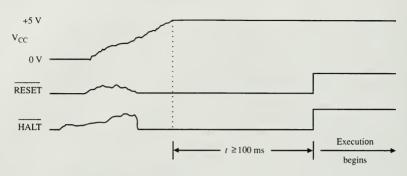

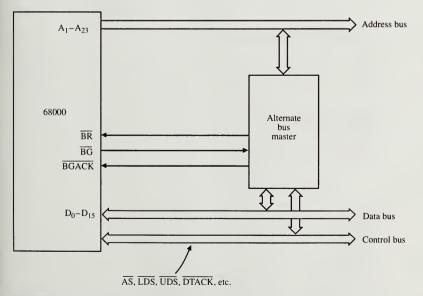

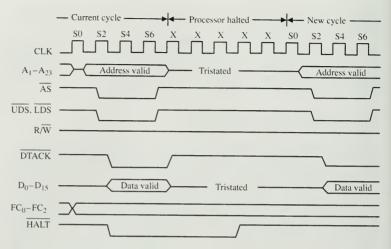

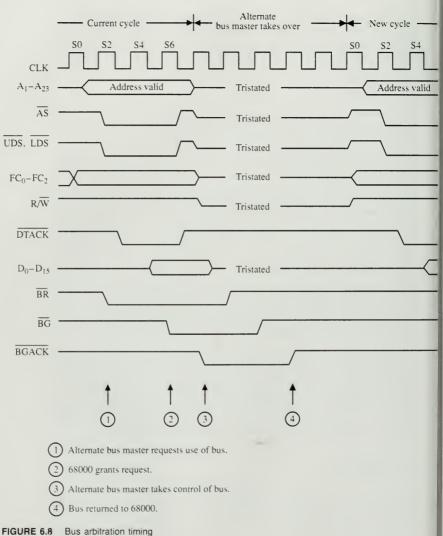

$\begin{array}{lll} V_{cc}, \, GND, \, and \, CLK & 170 \\ FC_{0}, \, FC_{1}, \, and \, FC_{2} & 171 \\ E, \, VMA, \, and \, VPA & 172 \\ \overline{RESET}, \, HALT, \, and \, \overline{BERR} & 173 \\ \overline{IPL}_{0}, \, \overline{IPL}_{1}, \, and \, \overline{IPL}_{2} & 175 \\ \overline{BR}, \, BG, \, and \, \overline{BGACK} & 175 \\ \overline{AS}, \, R/W, \, UDS, \, LDS, \, and \, DTACK & 177 \\ A_1 \, through \, A_{23}, \, D_0 \, through \, D_{15} & 178 \\ \end{array}$

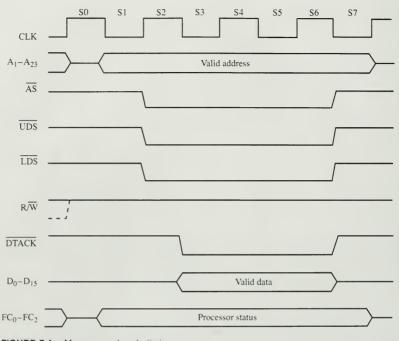

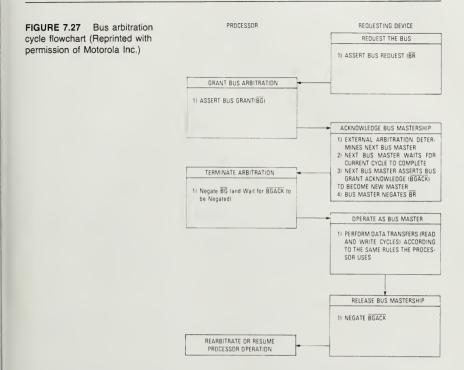

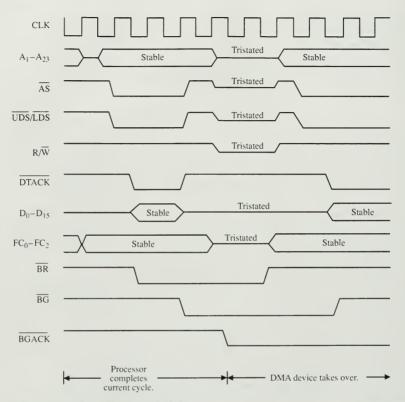

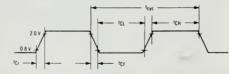

- 6.4 System Timing Diagrams 179 Processor HALT Timing 179 Bus Arbitration Timing 181

- 6.5 Summary 181 Study Questions 183

#### CHAPTER 7 Memory System Design

Objectives 187

- 7.1 Introduction 187

- 7.2 The 68000 Address and Data Buses 188

- 7.3 Bus Buffering 189

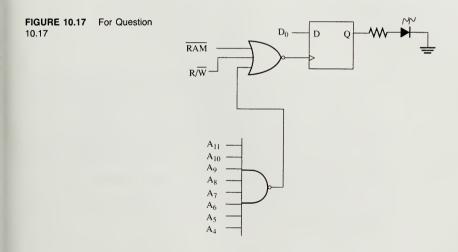

- 7.4 Accessing Memory 190

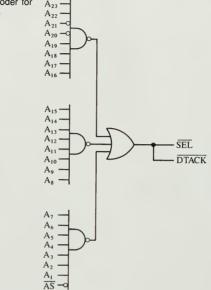

- 7.5 Designing a Memory Address Decoder 194

- 7.6 Partial-Address Decoding 201

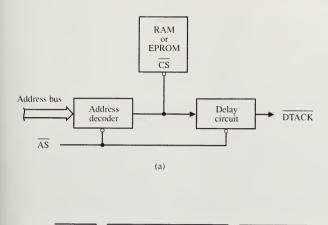

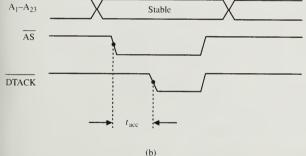

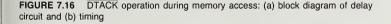

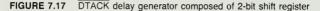

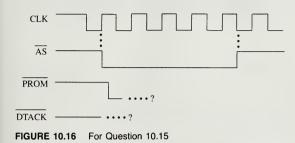

- 7.7 Generating DTACK 204

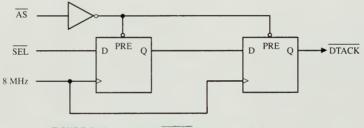

- 7.8 A Complete RAM/EPROM Memory 206

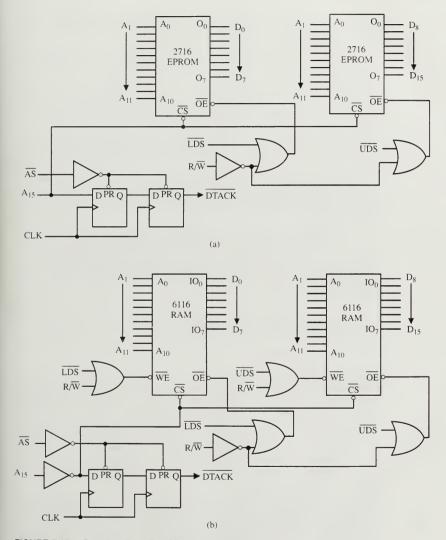

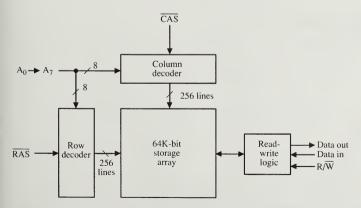

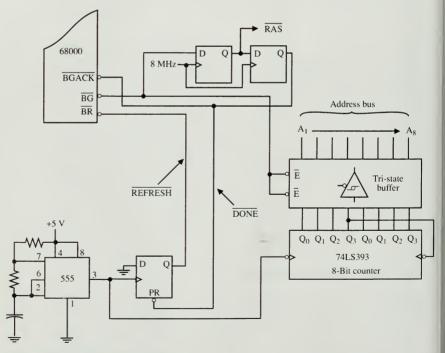

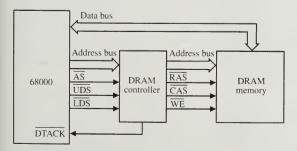

- 7.9 Dynamic RAM Interfacing 208

What is Dynamic RAM?

208

Accessing Dynamic RAM

209

Refreshing Dynamic RAM

212

A Dynamic RAM Controller

215

- 7.10 Direct Memory Access 216

- 7.11 Summary 216

- Study Questions 217

#### CHAPTER 8 I/O System Design

- Objectives 223

- 8.1 Introduction 223

- 8.2 Memory-Mapped I/O 224

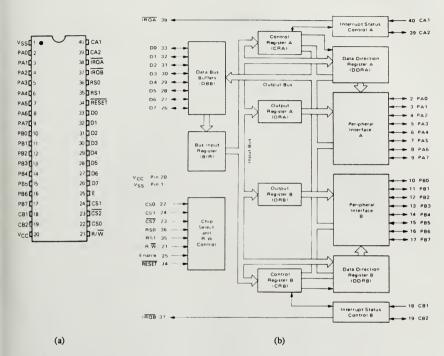

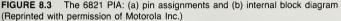

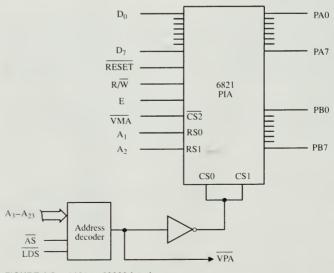

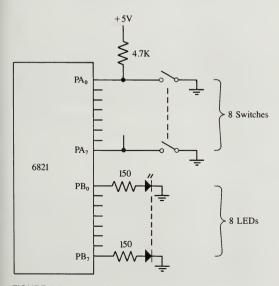

| 8.3 | Parallel-Data Transfer: The 6821 PIA                 | 224 |  |

|-----|------------------------------------------------------|-----|--|

|     | Programming the 6821 225<br>Interfacing the 6821 229 |     |  |

|     |                                                      |     |  |

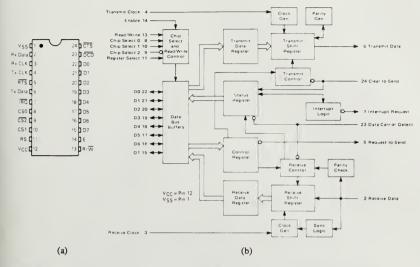

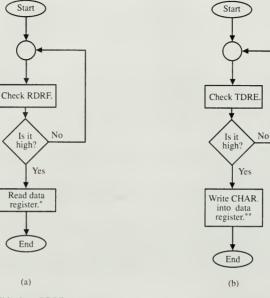

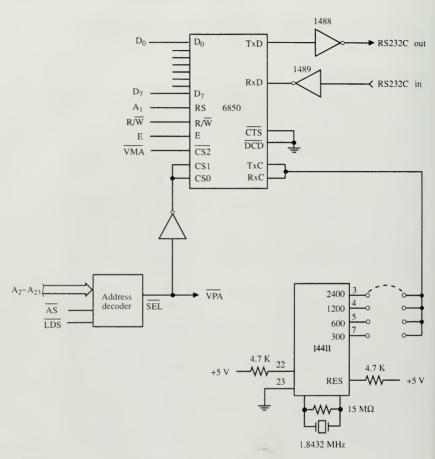

- 8.4 Serial Data Transfer: The 6850 ACIA 232 Programming the 6850 232 Interfacing the 6850 237

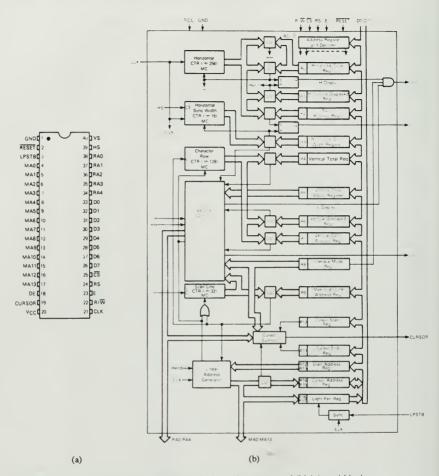

- 8.5 Memory-Mapped Video I/O: The 6845 CRT Controller 239

- 8.6 Summary 241 Study Questions 242

#### **CHAPTER 9**

#### Advanced Programming Using 68000 Peripherals

Objectives 245

- 9.1 Introduction 245

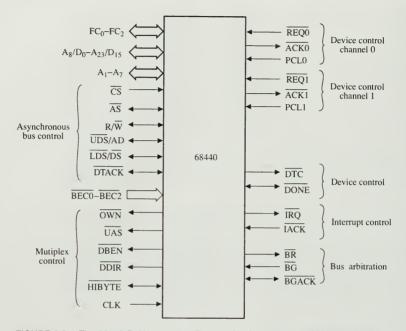

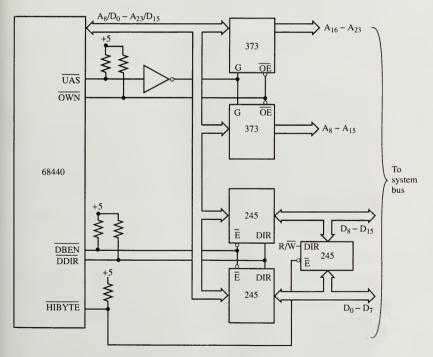

- 9.2 The 68440 Dual DMA Controller 246 Interfacing the 68440 247

- Programming the 68440 250

- 9.3 The 68451 Memory Management Unit 257 Interfacing the 68451 259 Programming the 68451 261

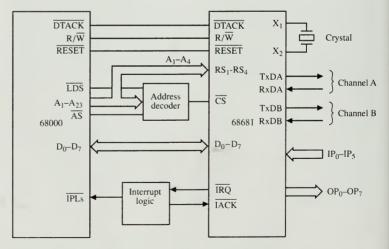

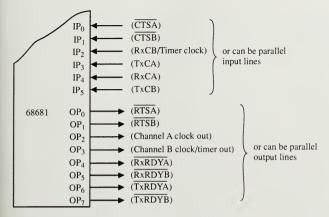

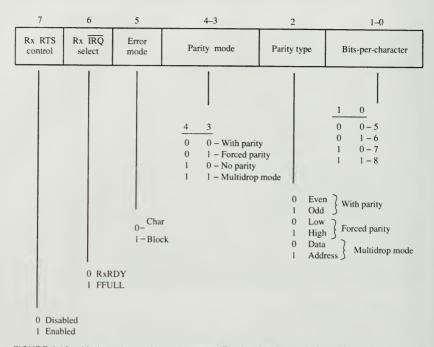

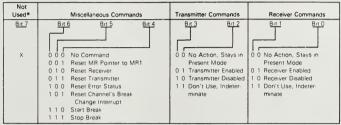

- 9.4 The 68681 Dual UART (Universal Asynchronous Receiver/Transmitter) 265 Interfacing the 68681 266 Programming the 68681 267

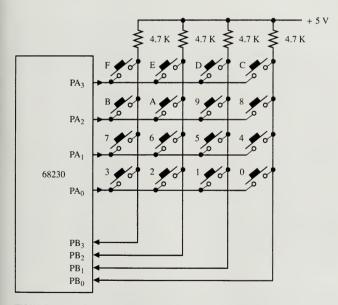

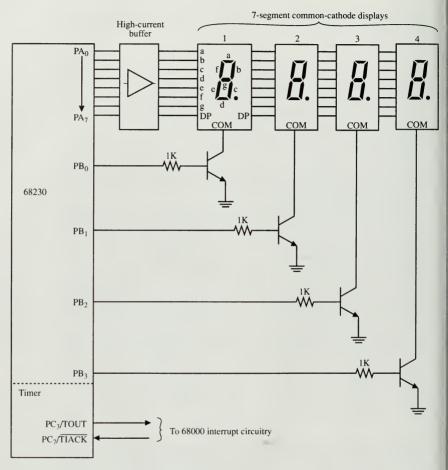

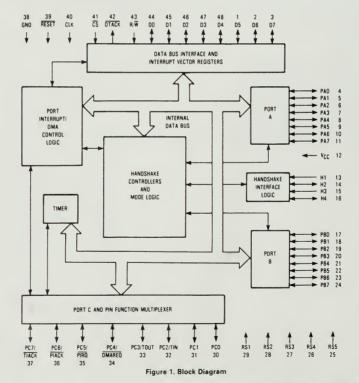

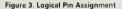

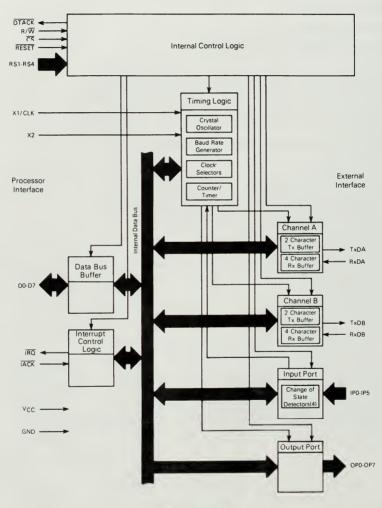

#### 9.5 The 68230 PI/T (Parallel Interface/Timer) 272 Interfacing the 68230 273 Programming the 68230 274

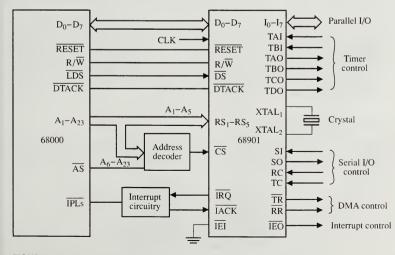

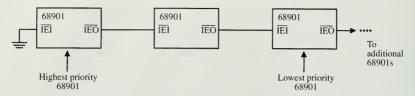

- 9.6 The 68901 Multifunction Peripheral 286 Interfacing the 68901 287 Programming the 68901 288

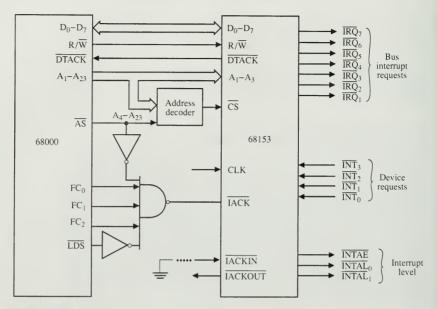

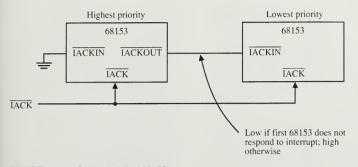

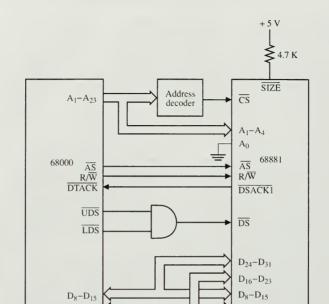

- 9.7 The 68153 Bus Interrupt Module 291 Interfacing the 68153 291

- Programming the 68153 292

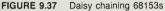

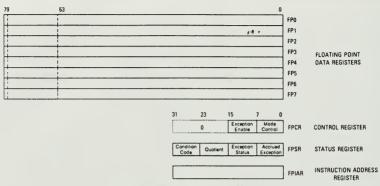

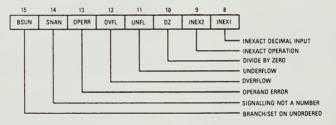

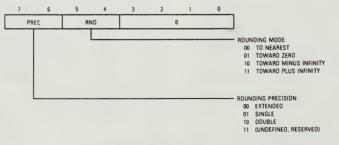

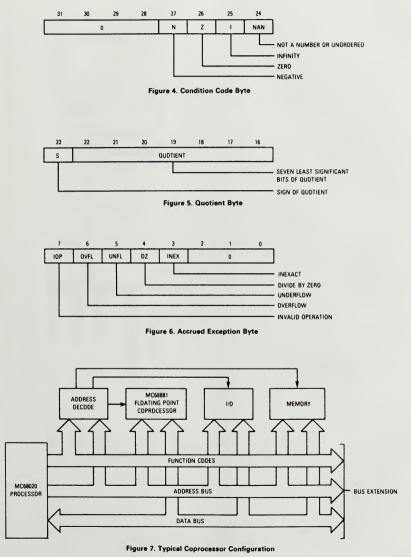

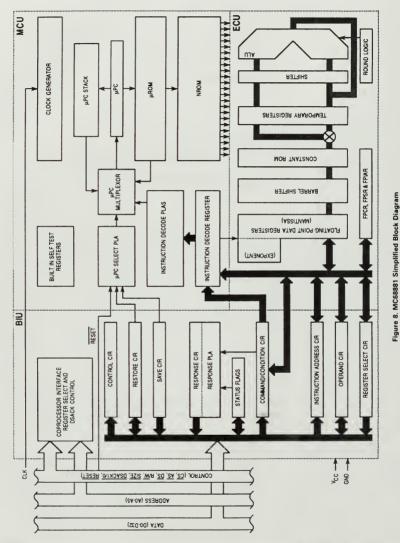

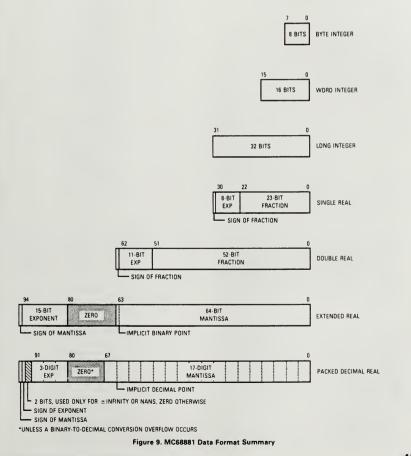

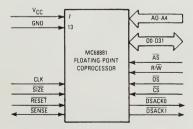

- 9.8 The 68881 Floating-Point Coprocessor 295 Interfacing the 68881 295 Programming the 68881 296

- 9.9 Interfacing with Non-Motorola Peripherals 301

9.10 A Summary of Other 68000-Based Peripherals 302

The 68652 Multiprotocol Communications Controller 302

- The 68184 Broadband Interface Controller 302 The 68824 Token-Passing Bus Controller 302 The 68452 Bus Arbitration Module 302

307

The 68590 LAN Controller for Ethernet303The 68465 Floppy Disk Controller303The 68486/68487 Raster Memory System303

9.11 Summary 303 Study Questions 303

#### **CHAPTER 10**

#### Building a Working 68000 System

Objectives 307

10.1 Introduction 307

- 10.2 Minimal System Requirements 308

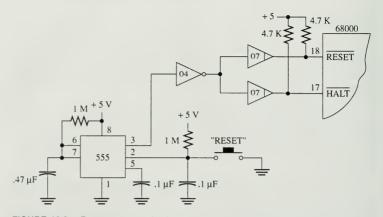

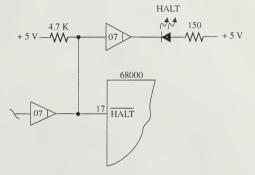

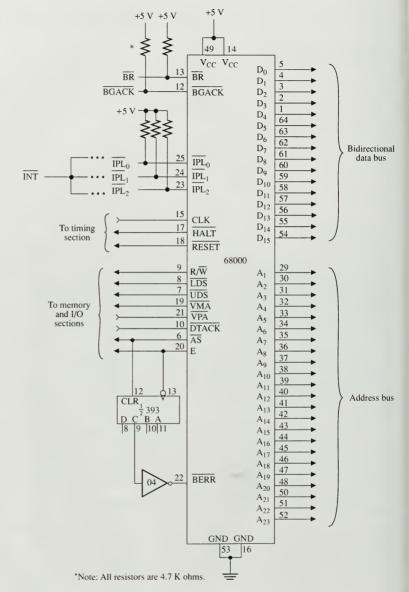

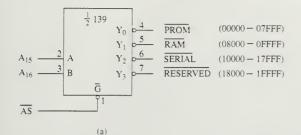

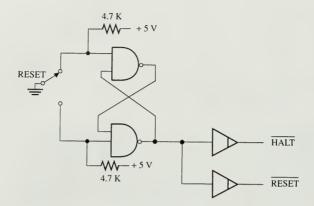

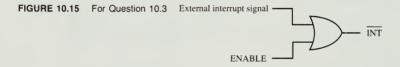

- **10.3** Designing the Hardware 308

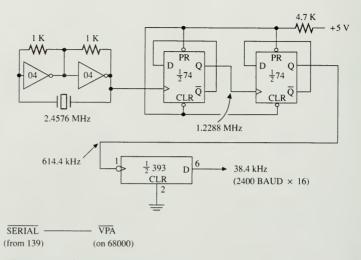

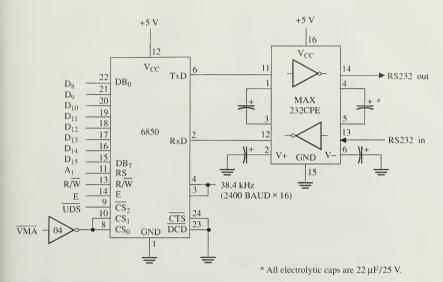

The Timing Section309The CPU Section311The Memory Section313The Serial Section316

#### 10.4 The Minimal System's Parts List 319

- 10.5 Construction Tips 320

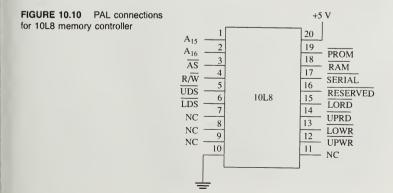

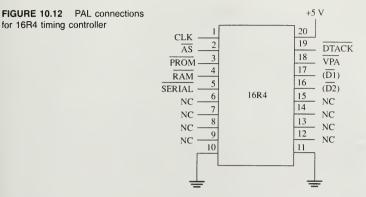

- 10.6 Using Programmable Logic in the Minimal System 321

- **10.7** Writing the Software Monitor 324

The Auxiliary Subroutines 325 The Monitor Commands 330 The Command Recognizer 330 The DUMP Routine 331 The EXECUTE Routine 333 The MOVE Routine 333 The PATCH Routine 333 The Body of the Monitor 334

- 10.8 Adding Commands to the Monitor 336

- 10.9 Example Programs 337

TV Typewriter 337 Improved TV Typewriter 337 Counter with Message 338 Hexadecimal Adder 338 Memory Search 338

10.10 Summary 339 Study Questions 339

APPENDIX A 68000 Data Sheets

APPENDIX B 68000 Instruction Set

| APPENDIX C<br>68000 Instruction Execution Times                 | 418 |

|-----------------------------------------------------------------|-----|

| APPENDIX D<br>68000 Peripheral Data Sheets                      | 428 |

| APPENDIX E<br>The 6800 Microprocessor: A Historical Perspective | 471 |

| INDEX                                                           | 487 |

## CHAPTER

# 1

## Microprocessor-Based Systems

#### Objectives

In this chapter you will learn about:

- The block diagram of a microprocessor-based system and the function of each section

- · The processing cycle of a microprocessor

- · The way software is used to initialize hardware and peripherals

- · The history of the microprocessor and of the different generations of computers

- · Some of the integrated circuits used in microprocessor-based systems

- · The calculator project

#### 1.1 INTRODUCTION

The invention of the microprocessor has had a profound impact on many aspects of our lives, since today even the most mundane chores are being accomplished under its supervision—something that allows us more time for other productive endeavors. Even a short list of the devices utilizing the microprocessor shows how dependent we have become on it:

- 1. Pocket calculators

- 2. Digital watches (some with calculators built in)

- 3. Automatic tellers (at banks and food stores)

- 4. Smart telephones

- 5. Compact disk players

- 6. Home security and control devices

- 7. Realistic video games

- 8. Talking dolls and other toys

- 9. VCRs

- 10. Home computers

The purpose of this chapter is to show how the microprocessor is used as a master controller in a small system. While no specific hardware or software will be presented, we will see what types of hardware functions are most desirable to include in a small system and what jobs must be performed by the software to control the hardware. Section 1.2 covers the block diagram of a microprocessor-based system and explains each functional unit. Section 1.3 reviews the basic operation of a microprocessor. Section 1.4 discusses the hardware and software requirements of a small microprocessor control system. Section 1.5 shows how the microprocessor has evolved over time, from the initial 4-bit machines to today's 16- and 32-bit processors. Section 1.6 presents a number of special logic gates well suited for use in a microprocessor-based system. Finally, an introduction to the calculator project is given in Section 1.7.

#### 1.2 SYSTEM BLOCK DIAGRAM

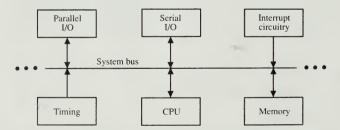

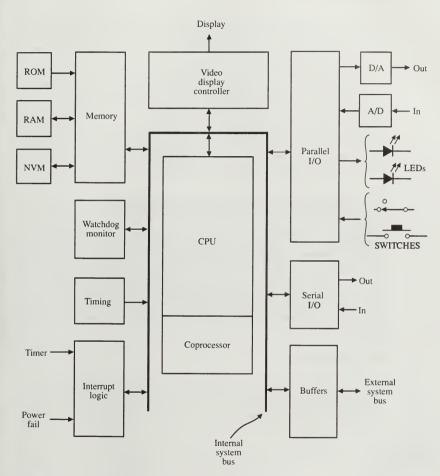

Any microprocessor-based system must of necessity have some standard elements such as memory, timing, and input/output (I/O). Depending on the application, other exotic circuitry may be necessary as well. Analog-to-digital (A/D) converters and their counterpart, digital-to-analog (D/A) converters, interval timers, math coprocessors, complex interrupt circuitry, speech synthesizers, and video display controllers are just a few of the special sections that may also be required. Figure 1.1 depicts a block diagram of a system containing some of the more standard circuitry and functions normally used.

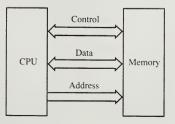

As the figure shows, all components communicate via the **system bus**. The system bus is composed of the processor address, data, and control signals. The **central processing unit** (**CPU**) is the heart of the system, the master control-

FIGURE 1.1 Standard block diagram of a microprocessor-based system

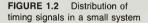

ler of all operations that can be performed. The CPU executes instructions that are stored in the **memory** section. For the sake of future expansion, the system bus is commonly made available to the outside world (through a special connector). Devices may then be added easily as the need arises. Commercial systems have predefined buses that accomplish this. All devices on the system bus must communicate with the processor, usually within a tightly controlled period of time. The **timing** section governs all system timing and thus is really responsible for the proper operation of all system hardware. The timing section usually consists of a crystal oscillator and timing circuitry (counters designed to produce the desired frequencies) set up to operate the processor at its specified clock rate. Using a high-frequency crystal oscillator and dividing it down to a lower frequency provides for greater stability. Figure 1.2 shows the distribution of timing signals throughout the microprocessor-based system. The timing section supplies timing signals for a number of different sections.

The CPU section consists of a microprocessor and the associated logic circuitry required to enable the CPU to communicate with the system bus. These logic elements may consist of data and address bus drivers, a bus controller to generate the correct control signals, and possibly a math coprocessor. **Coprocessors** are actually microprocessors themselves; their instruction set consists mainly of simple instructions for transferring data and complex instructions for performing a large variety of mathematical operations. Coprocessors perform these operations at very high clock speeds with a great deal of precision (80-bit results are common). In addition to the basic add/subtract/multiply/ divide operations, coprocessors are capable of finding square roots, logarithms, a host of trigonometric functions, and more.

The actual microprocessor used depends on the complexity of the task that will be controlled or performed by the system. Simple tasks require nothing more complicated than an 8-bit CPU. A computerized cash register would be a good example of this kind of system. Nothing more complicated than binary coded decimal (BCD) addition and subtraction—and possibly some record keeping—is needed. But for something as complex as a flight control computer for an aircraft or a digital guidance system for a missile, a more powerful 16- or 32-bit microprocessor must be used.

The memory section usually has two components: read-only memory (ROM) and random access memory (RAM). Some systems may be able to work properly without RAM, but all require at least a small amount of ROM. The ROM is included to provide the system with its intelligence, which is ordinarily needed at start-up (power-on) to configure or initialize the peripherals, and sometimes to help recover from a catastrophic system failure (such as an unexpected power failure). Some systems use the ROM program to download the main program into RAM from a larger, external system, such as a personal computer (PC) or a mainframe computer. In any event, provisions are usually made for adding additional ROM as the need arises.

There are three types of RAM. For small systems that do not process a great deal of data, the choice is static RAM. Static RAM is fast and easy to interface but comes in small sizes of 32 kilobytes (KB) or less as of this writing. Larger memory requirements are usually met by using dynamic RAM, a different form of memory that has high density (256K bits per chip or more) but that unfortunately requires numerous refreshing cycles to retain the stored data. Even so, dynamic RAM is the choice when large amounts of data must be stored, as in a system gathering seismic data at a volcano or in one receiving digitized video images from a satellite.

Both static and dynamic RAM lose their information when power is turned off, which may cause a problem in certain situations. Previous solutions involved adding battery backup circuitry to the system to keep the RAMs supplied with power during an outage. But batteries can fail, so a better method was needed. Thus came the invention of **nonvolatile memory** (**NVM**), which is memory that retains its information even when power is turned off. **NVM** comes in small sizes and therefore is used to store only the most important system variables in the event of a power outage.

We will not consider other storage media such as disks or tape, since they require complex hardware and software to operate and are not required in most control applications.

When a microprocessor is used in a control application, sometimes the system must respond to special external circumstances. For example, a power failure on a computer-controlled assembly line requires immediate attention by the system, which must contain software designed to handle the unexpected event. The event actually *interrupts* the processor from its normal program execution in order to service the unexpected event. The system software is designed to handle the power-fail interrupt in a certain way and then return to the main program. An interrupt thus is a useful way to grab the processor's attention, get it to perform a special task, and then resume execution from where it left off.

Not all types of interrupts are unexpected. Many are used to provide the system with useful features such as real-time clocks, multitasking capability, and fast input/output operations.

The interrupt circuitry needed from system to system will vary depending on the application. A system used for keeping time only has to use a single interrupt line connected to a timing source. A more complex system, such as an assembly line controller, which may need to monitor multiple sensors, switches, and other items, may require many different prioritized interrupts and would therefore need more complex interrupt circuitry.

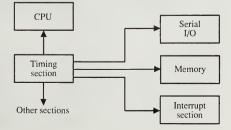

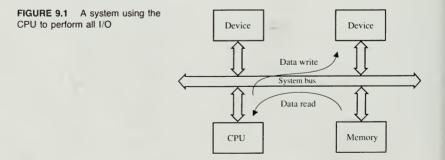

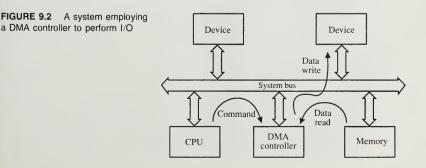

Some systems may require serial I/O for communication with an operator's console or with a host computer. In Figure 1.3 we see how a small system might communicate with other devices or systems via serial communication. While this type of communication is slow, it has the advantage of simplicity: Only two wires (for receive and transmit) plus a ground are needed. Serial communication is easily adapted for use in fiber-optic cables. Parallel I/O, on the other hand, requires more lines (at least eight) but has the advantage of being very fast. A special parallel operation called **direct memory access** (DMA) is used to transfer data from a hard disk to a microcomputer's memory. Other uses for parallel I/O involve reading switch information, controlling indicator lights, and transferring data to A/D and D/A converters and other types of parallel devices.

All of these sections have their uses in a microprocessor-based system. Whether or not they are actually utilized depends on the designer and the application.

FIGURE 1.3 Serial communication possibilities in a small system

#### **1.3 MICROPROCESSOR OPERATION**

No matter how complex microprocessors become, they will still follow the same pattern of operations during program execution: endless fetch, decode, and execute cycles. During the fetch cycle the processor loads an instruction from memory into its internal instruction register. Some advanced microprocessors load more than one instruction into a special buffer to decrease program execution time. The idea is that while the microprocessor is decoding the current instruction, other instructions can be read from memory into the instruction cache, a special type of internal high-speed memory. In this fashion the microprocessor performs two jobs at once, thus saving time.

During the decode cycle the microprocessor determines what type of instruction has been fetched. Information from this cycle is then passed to the execute cycle. To complete the instruction, the execute cycle may need to read more data from memory or write results to memory.

While these cycles are proceeding, the microprocessor is also paying attention to other details. If an interrupt signal arrives during execution of an instruction, the processor will usually latch onto the request, holding off on interrupt processing until the current instruction finishes execution. The processor also monitors other signals such as WAIT, HOLD, or READY inputs. These are usually included in the architecture of the microprocessor so that slow devices, such as memories, can communicate with the faster processor without loss of data.

Most microprocessors will also include a set of control signals that allow external circuitry to take over the system bus. In a system where multiple processors share the same memory and devices, these types of control signals are necessary to resolve **bus contention** (two or more processors needing the system bus at the same time). Multiple-processor systems are becoming more popular now as we continue to strive toward faster execution of our programs. **Parallel processing** is a term often used to describe multiple-processor systems and their associated software.

Special devices called **microcontrollers** are often used in simple control systems because of their many features. Microcontrollers are actually soupedup microprocessors with built-in features such as RAM, ROM, interval timers, parallel I/O ports, and even A/D converters. Microcontrollers are not used for really big systems, however, because of their small instruction sets. Unfortunately, we have yet to get everything we want on a single chip!

#### 1.4 HARDWARE/SOFTWARE REQUIREMENTS

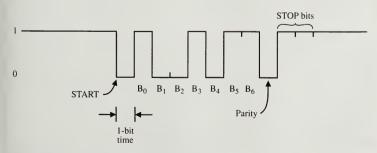

We saw earlier that it is necessary to have at least some ROM in our system to take care of peripheral initialization. What type of initialization is required by the peripherals? The serial device must have its BAUD rate, parity, and number of data and stop bits programmed. Parallel devices must be configured because most allow the direction (input or output) of their I/O lines to be programmed in many different ways. It is then necessary to set the direction of these I/O lines when power is first applied. For a system containing a digitalto-analog converter it may be important to output an initial value required by the external hardware. Since we can never assume that correct conditions exist at power-on, the microprocessor is responsible for establishing them.

Suppose a certain system contains a video display controller. Start-up software must select the proper screen format and initialize the video memory so that an intelligent picture (possibly a menu) is generated on the screen of the display. If the system uses light-emitting diode (LED) displays or alphanumeric displays for output, they must be properly set as well. High-reliability systems may require that memory be tested at power-on. While this adds to the complexity of the start-up software and the time required for initialization, it is a good practice to follow. Bad memory devices will certainly cause a great deal of trouble if they are not identified.

Other systems may employ a special circuit called a **watchdog monitor**. This circuit operates like this: During normal program execution the watchdog monitor is disabled. Should the program veer from its proper course, the monitor will automatically reset the system. A simple way to make a watchdog monitor is to use a binary counter, clocked by a known frequency. If the counter is allowed to increment up to a certain value, the processor is automatically reset. The software's job, if it is working correctly, is to make sure that the counter never reaches this count. A few simple logic gates can be used to clear the counter microprocessor control, possibly whenever the CPU examines a certain memory location.

For flexibility, the system may have been designed to download its main program from a host system. If this is the case, the system software will be responsible for knowing how to communicate with the host and place the new program into the proper memory locations. To guarantee that the correct program is loaded, the software should also perform a running test on the incoming data, requesting the host to retransmit portions of the data whenever it detects an error.

Sometimes preparing for a power-down is as important as doing the startup initialization. A power supply will quite often supply voltage in the correct operating range for a few milliseconds after the loss of AC. It is during these few milliseconds that the processor must execute the shutdown code, saving important system data in nonvolatile RAM or doing whatever is necessary for a proper shutdown. If the system data can be preserved, it may be possible to continue normal execution when power is restored.

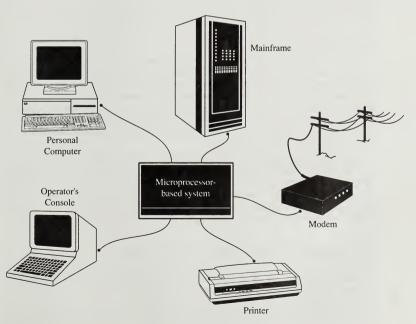

For systems that will be expanded in the future, the system bus must be made available to the outside world. To protect the internal system hardware, all signals must be properly buffered. This involves using tristate buffers or similar devices to isolate the internal system bus from the bus available to the external devices. Sometimes optoisolators are used to completely separate the internal system signals from the external ones. The only connection in optoisolators is a beam of light, which makes them ideal when electrical isolation is required. Figure 1.4 sums up all of these concepts with an expanded block diagram of a microprocessor-based control system. Notice once again that all devices in the system communicate with the CPU via the system bus.

#### 1.5 EVOLUTION OF MICROPROCESSORS

We have come a long way since the early days of computers, when ENIAC (for Electronic Numerical Integrator and Computer) was state of the art and occupied thousands of square feet of floor space. Constructed largely of vacuum tubes, it was slow, prone to breakdown, and performed a limited number of instructions. Even so, ENIAC ushered in what was known as the **first generation** of computers.

Today, thanks to advances in technology, we have complete computers that fit on a piece of silicon no larger than your fingernail and that far outperform ENIAC.

When the transistor was invented, computers shrank in size and increased in power, leading to the second generation of computers. Third-generation computers came about with the invention of the integrated circuit, which allowed hundreds of transistors to be packed on a small piece of silicon. The transistors were connected to form logic elements, the basic building blocks of digital computers. With third-generation computers we again saw a decrease in size and increase in computing power. Machines like the 4004 and 8008 by Intel found some application in simple calculators, but they were limited in power and addressing capability. When improvements in integrated circuit technology enabled us to place thousands of transistors on the same piece of silicon, computers really began to increase in power. This new technology, called large-scale integration (LSI), is even faster than the previous mediumand small-scale integration (MSI and SSI) technologies, which dealt with only tens or hundreds of transistors on a chip. LSI technology has created the fourth generation of computers that we use today. An advanced form of LSI technology, VLSI, meaning very-large-scale integration, is also being used to increase processing power.

The first microprocessors that became available with third-generation computers had limited instruction sets and thus restricted computing abilities. Although they were suitable for use in electronic calculators, they simply did not have the power needed to operate more complex systems, such as guidance systems or scientific applications. Even some of the early fourth-generation microprocessors had limited capabilities because of the lack of addressing modes and instruction types. Eight-bit machines like the 8080, Z80, and 6800 were indeed more advanced than previous microprocessors, but they still did not possess multiply and divide instructions. How frustrating and time consuming to have to write a program to do these operations when needed!

Within the last decade microprocessor technology has improved tremendously, however. Sixteen-bit processors can now multiply and divide, operate on many different data types (4-, 8-, 16-, and 32-bit numbers), and address

FIGURE 1.4 Expanded block diagram of a microprocessor-based system

*millions* of bytes of information. Processors of the 1970s were limited to 64KB, a small amount of memory by today's standards.

Each new microprocessor to hit the market boasts a fancier instruction set and faster clock speed, and indeed our needs for faster and better processors keep growing. A new technology called RISC (for reduced instruction set computer) has recently gained acceptance. This technology is based on the fact that most microprocessors utilize only a small portion of their entire instruction set. By designing a machine that uses only the more common types of instructions, processing speed can be increased without the need for a significant advance in integrated circuit technology.

Why the need for superfast machines? Consider a microprocessor dedicated to displaying three-dimensional color images on a video screen. Rotating the three-dimensional image around an imaginary axis in real time (in only a few seconds or less) may require millions or even billions of calculations. A slow microprocessor would not be able to do the job.

Eventually we will see fifth-generation computers. The whole artificial intelligence movement is pushing toward that goal, with the desired outcome the production of a machine that can think. Until then we will have to make the best use of the technology we have available.

#### 1.6 SPECIAL GATES FOR MICROCOMPUTER USE

Unfortunately we cannot simply throw a CPU, memory chips, and a handful of peripherals together and come up with a working computer. Other chips are needed to control the system timing and support communication between the peripherals and the processor. In this section we will examine some of the most common integrated circuits used in the design of a microprocessor-based system. Since most of the available microprocessors are designed for TTL (transistor transistor logic) compatibility, we will examine TTL integrated circuits section.

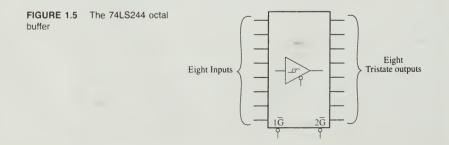

#### The Octal Buffer

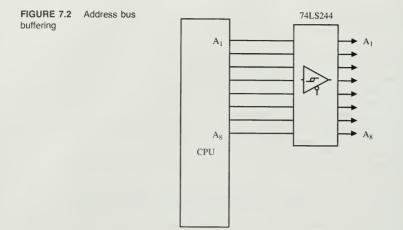

Figure 1.5 shows the schematic diagram of a commercial 74LS244 octal buffer. This chip is very useful in many ways. It can be used to buffer address lines and control the flow of information onto a data bus. When a system is designed with multiple memory devices, all of which require address and data lines, the

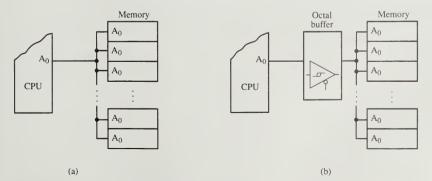

fan-out of the microprocessor's output lines can easily be exceeded. Having a CPU address line drive three or four inputs is not unreasonable, but trying to drive twenty or twenty-five inputs with an unbuffered output will certainly not work. This is because of the output current limitation of the processor's signal lines; most CPUs cannot supply more than a few mA. The 74LS244 is designed to correct this problem. Each of its outputs is able to sink 24 mA, more than enough to satisfy our design needs.

The octal buffer is placed *between* the CPU and the memory chips (or peripherals), as we can see in Figure 1.6. This design actually serves two purposes. It not only provides the necessary drive capability to the CPU address lines, but also serves to isolate the CPU from the system bus. If we consider a system that will have other devices (or processors) using its system bus, the host CPU can be easily disconnected by tristating its octal buffers.

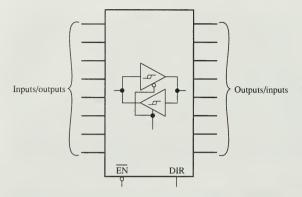

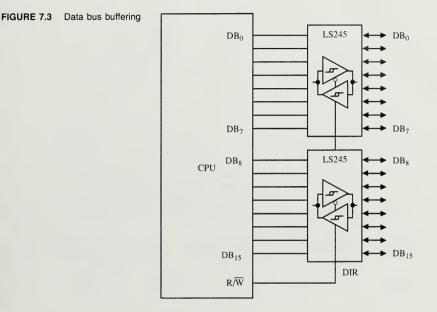

#### The Octal Bus Transceiver

The 74LS245 is an octal bus transceiver. Figure 1.7 shows that this device is used to buffer signals in two directions, making it suitable for use in <u>buffering</u> a bidirectional data bus. The transceiver is controlled by two inputs:  $\overline{EN}^*$  (enable) and DIR (direction). If  $\overline{EN}$  is high, the transceiver is tristated in both directions and will not pass data either way. When  $\overline{EN}$  is low, data is passed in the direction specified by DIR.

Normally the CPU's  $R/\overline{W}$  line is used to control the direction of data through the transceiver. When  $R/\overline{W}$  is high, the 74LS245 passes data into the processor. When  $R/\overline{W}$  is low, data is output from the processor.

\*The overbar in EN is used to show that the asserted (active) state of this signal is low. EN would be an active high signal.

FIGURE 1.6 Microprocessor address line: (a) cannot drive required number of memory devices and (b) drives all memory devices via octal buffer

FIGURE 1.7 The 74LS245 octal bus transceiver

The 74LS245's 24-mA drive capability on each output makes it ideal for driving the CPU's bidirectional data bus.

#### The Octal D-Type Flip-Flop

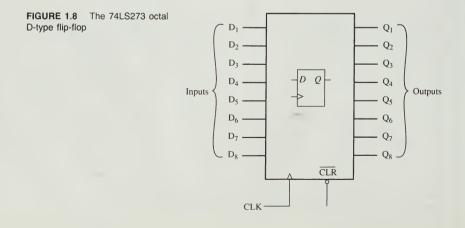

Figure 1.8 shows the schematic of a 74LS273 octal D-type flip-flop. This device is very useful when constructing 8-bit output ports (or 16-bit ports by using two devices). All eight flip-flops share a common clock and clear line. This makes it easy to either capture a byte of data or clear all outputs at the same

time. When only 8 bits must be latched, the 74LS273 is a perfect choice, being cheaper and easier to use than a full-blown parallel device.

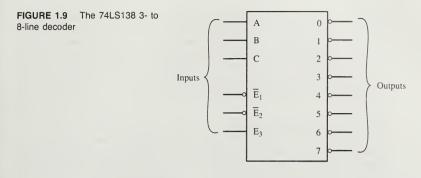

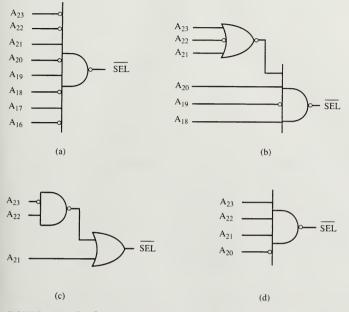

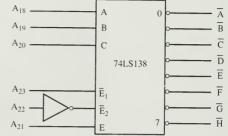

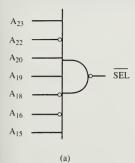

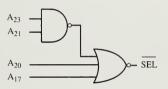

### The 3- to 8-Line Decoder

The 74LS138 3- to 8-line decoder is very useful when designing memory circuitry. Figure 1.9 shows the schematic for this device, which activates one of its outputs at a time, depending on the binary code present at the inputs. When used in a memory circuit, the A, B, and C inputs will be connected to three upper address lines (with the lower address lines going directly to the ROM and RAM chips). The outputs will be connected to the CE inputs of the memory chips. This will cause different memory devices—or maybe none—to be enabled, depending on the condition of the upper address lines.

### The Priority Encoder

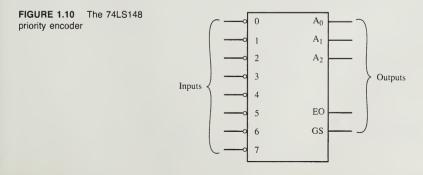

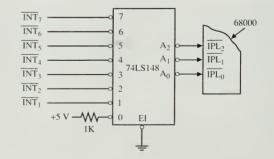

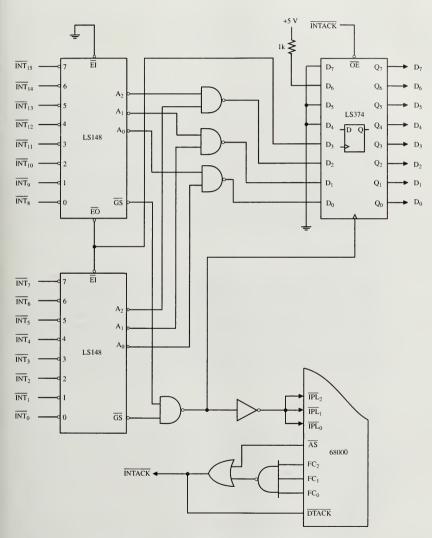

The 74LS148 8- to 3-line priority encoder, pictured in Figure 1.10, finds application in interrupt circuitry. Quite often a system will be presented with a

number of interrupt signals. What should the processor do when more than one interrupt signal is active at the same time? The 74LS148 solves the problem by prioritizing the interrupts. Normally a single input will go to the low state, causing the  $A_0$  through  $A_2$  outputs to represent the binary code of the input that became active. If two or more inputs go low at the same time, the outputs will represent the number of the highest active input (for example, this would be input 5, if 5, 4, and 2 are all active).

### The Parity Generator/Checker

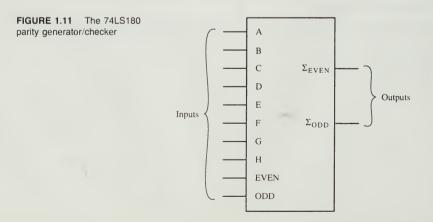

Figure 1.11 shows the schematic diagram of the 74LS180 even/odd parity generator/checker. This device is most useful in memory circuitry that requires high reliability. Instead of storing just 8-bit values in each memory location, 9 bits are used, with one dedicated to the parity of the stored data. When the CPU writes data to a memory location, the 74LS180 generates the parity bit for the data, which is then stored. When the processor reads the same location, the parity of the 8 data bits is recomputed by the 74LS180 and compared with the parity bit that was stored. A **parity error** results when the two bits fail to match. This type of memory failure is usually catastrophic because there is no way to recover the good data.

Parity generators/checkers are also used in serial transmission circuitry, and are usually contained within the transmitter/receiver sections.

### 1.7 THE CALCULATOR PROJECT

Although the following chapters contain numerous hardware and software design examples and applications, a book-long example called the *calculator*

*project* will be utilized to show how an entire 68000-based system is developed. The common features and operations of a calculator are known to all, and this familiarity is used to bring in new concepts and ideas as they are presented in each chapter. For example, the display and keypad sections of the calculator are designed in the chapter on peripherals. The calculator's mathematical routines are developed in the chapters on programming and exceptions. Throughout the project, numerous questions are asked and answered to guide the design toward a final product. Room for improvement is deliberately included, to encourage original thought.

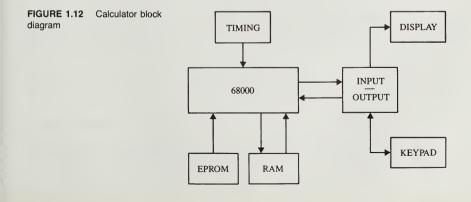

A simplified block diagram of the calculator is shown in Figure 1.12. Specific interfaces for the RAM, EPROM, and input/output sections will be designed, as will the software to run the entire system. Since the design is broken up into specific sections, every effort is made to ensure that out-of-sequence treatment does not affect the reader's understanding of any single section.

### 1.8 SUMMARY

In this chapter we have examined the operation of microprocessor-based systems. We saw that the complexity of the hardware, and thus of the software, is a function of the type of application. Through the use of many different types of peripherals, such as parallel and serial devices, analog-to-digital converters, and others, a system can be tailored to perform almost any job. We also reviewed the basic fetch, decode, and execute cycle of a microprocessor, and examined the other duties the CPU performs, one of which was interrupt handling.

We also covered the initialization requirements of peripherals used in a microprocessor-based system, and why it is necessary to perform initializa-

tion in the first place. Other types of hardware and software requirements were also examined, such as the use of a watchdog monitor and a nonvolatile memory.

Four different generations of computers were presented and their differences highlighted. Current computing trends dealing with parallel processing and artificial intelligence were also introduced.

We then looked at a number of different TTL gates that for various reasons find their way into many microcomputer designs. This was followed by a description of the calculator project, a hardware/software design concept that will reappear in the following chapters.

### STUDY QUESTIONS

- 1. Make a list of 10 additional products containing microprocessors that we use everyday.

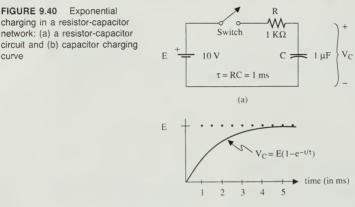

- 2. Why would an oscillator circuit utilizing a resistor-capacitor network to control its frequency be unstable and unsuitable for use in a microprocessor-based system?

- 3. Speculate on the uses for timing signals in the serial I/O, memory, and interrupt sections.

- 4. Why do coprocessors enhance the capabilities of an ordinary CPU?

- 5. Draw a block diagram for a computerized cash register. The hardware should include a numerical display, a keyboard, and a compact printer.

- 6. What kind of initialization software would be required for the cash register of Question 5?

- 7. What would be the difference in system RAM requirements for two different cash registers, one without record keeping and one with?

- 8. What type of information should be stored in NVM during a power failure in a system designed to control navigation in an aircraft?

- **9.** What types of interrupts may be required in a control system designed to monitor all doors, windows, and elevators in an office complex?

- 10. Name some advantages of downloading the main program into a microprocessorbased system. Are there any disadvantages?

- 11. Suppose that a number of robots making up a portion of an automobile assembly line are connected to a master factory computer. What kinds of information might be passed between the factory computer and the microprocessors controlling each robot?

- 12. A certain hard disk transfers data at the rate of 8 million bits per second. Explain why the CPU would not be able to perform the transfer itself, thus requiring the use of a DMA controller.

- 13. What kinds of problems arise if two devices attempt to use the system bus at the same time?

- Explain how two microprocessors might be connected so that they share the same memory and peripherals.

- 15. Suppose that three microprocessors are used in the design of a new video game containing color graphics and complex sounds. How might each microprocessor function?

- 16. Why did processing speed increase with each new generation of computers?

- 17. List five different applications that might need the fast computing power of a RISCbased machine.

- 18. One reason 16-bit processors are faster than 8-bit machines is that they operate on twice as many data bits at the same time. Why doesn't everyone using an 8-bit machine just switch over to a 16-bit processor?

- 19. An upward-compatible microprocessor is one that can execute instructions from earlier models. How would a designer of the new CPU implement upward compatibility?

- 20. Explain how an octal buffer may be used to load information from a set of switches onto the CPU data bus.

- 21. Show how an octal latch could be used to control a 7-segment display (including the decimal point).

- 22. Why use a 74LS244 instead of a 74LS245 to buffer a CPU's address lines?

- **23.** How can two groups of three different signals each be connected to a priority encoder, so that one group has a priority of 6 and the other a priority of 3?

- 24. Why would a parity checker only recognize single, or odd-numbered, bit errors?

- 25. What advantages does a microcontroller have over a microprocessor? What disadvantages?

# CHAPTER

# 2

# An Introduction to the 68000 Microprocessor

## Objectives

In this chapter you will learn about:

- The register set of the 68000

- · The addressing capabilities and data types that may be used

- · The different addressing modes and instruction types available

- The usefulness of exceptions

- Some of the hardware and software advantages of the 68000

- Some of the differences between the 68000 and the 68008/10/20/30 microprocessors

# 2.1 INTRODUCTION

The introduction of the 68000 into the arena of microprocessors came at a time when we were reaching the limits of what an 8-bit machine could do. With their restricted instruction sets and addressing capabilities, it was obvious that something more powerful was needed. The 68000 contains instructions previously unheard of in 8-bit machines, a very large address space, many different addressing modes, and an architecture that easily lends itself to multiprocessing or multitasking (running many programs simultaneously).

In this chapter we will examine the features of the 68000 microprocessor and its cousins, the 68008, 68010, 68020, and 68030. Only basic material will be covered, leaving the hardware and software details for upcoming chapters. From reading this chapter you should become aware that the 68000 is a machine with many possibilities. Section 2.2 covers the software model of the 68000. Section 2.3 provides a brief functional description of the processor. Section 2.4 explains the various data types that may be used (8-, 16-, and 32-bit data sizes for many instructions). Section 2.5 lists the numerous instruction types that comprise the 68000's instruction set. Section 2.6 describes the 68000's 14 different addressing modes. Section 2.7 introduces the concept of an exception and lists a few of the many types of exceptions possible. Section 2.8 compares the 68000 with another 16-bit machine—the 8086—and states its advantages. Sections 2.9 through 2.12 deal with the 68008, 68010, 68020, and 68030 microprocessors, respectively, describing them and listing their architectural differences. Section 2.13 begins the calculator project.

### 2.2 THE SOFTWARE MODEL OF THE 68000

The 68000 microprocessor contains eight data registers, referred to as D0 through D7, eight address registers, A0 through A7, a program counter, and a status register. All registers except for the status register are 32 bits in length.

Technically speaking, there are two A7 address registers. One makes up the **user** stack pointer and the other the **supervisor** stack pointer. These two processing states, user and supervisor, are what make the 68000 an ideal processor for applications involving multiprogramming, multitasking, and the creation of operating systems. Programs running in the user state are denied access to a few special instructions, two of them being STOP and RESET. Trying to execute these privileged instructions in the user state causes an error condition. The processor responds to this error condition by entering the supervisor state and taking appropriate action, determine by software, in a routine called an **exception handler**.

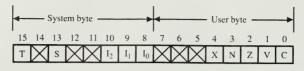

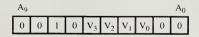

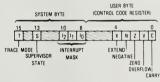

The processing state is determined by a special bit in the status register. Figure 2.1 portrays the details of the 16-bit status register. The lower eight bits form the user byte. These bits contain the five status bits that may be directly tested by the programmer. These five bits are commonly called **condition codes**, or **flags**. X, N, Z, V, and C represent the processor's extended, negative, zero, overflow, and carry conditions, as determined by previous instruction execution. The upper eight bits make up the system byte. These bits are unavailable to the programmer unless the processor is in the supervisor state. The processing state is controlled by the S bit (0 for user, 1 for supervisor), and there are special instructions available for manipulating this bit. A

FIGURE 2.1 68000 status register

nice addition to the 68000, and something not available on previous 8-bit machines, is the T bit, which enables trace mode in the processor. Trace mode makes it possible to single-step through a program, instruction by instruction. This is very useful when debugging a new piece of code. A trace is actually an **exception** that allows the user to debug (or monitor execution of) an executing program.

$I_0$  through  $I_2$  make up the processor's interrupt mask. They are used to determine what levels of external interrupts the 68000 will respond to.

## 2.3 A FUNCTIONAL DESCRIPTION OF THE 68000

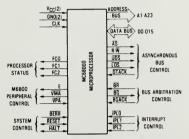

The 68000 is most commonly referred to as a 16-bit machine, even though it can perform a wide variety of operations on 32-bit data words. All external data enters the CPU on 16 bidirectional data lines ( $D_0$  through  $D_{15}$ ). The 68000's 23 address lines ( $A_1$  through  $A_{23}$ ), together with two other signals— UDS and LDS (for upper and lower data strobe)—give the processor the ability to address over 16 *million* bytes of memory. This large addressing space makes the handling of large databases convenient, and also supports the development of multiuser systems. Suppose that a customer needs a word processing system capable of supporting 16 users simultaneously. The 68000 makes it possible to give each user almost 1 million bytes of memory, enough storage space to hold approximately 218 pages of text (with each page containing 60 lines of 80 characters each). Some memory must, of necessity, be reserved for the operating system functions.

Other signals on the 68000 provide for two different types of data transfers: synchronous and asynchronous, with asynchronous being faster. The synchronous transfers enable the 68000 to communicate with peripherals designed for the earlier 6800 microprocessor.

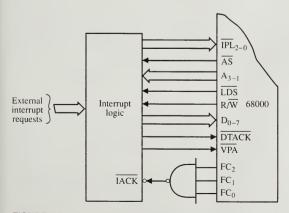

Furthermore, the 68000 will respond to seven levels of external hardware interrupts, and has bus arbitration logic that supports its use in multiprocessor systems.

All of these features come in a 64-pin package that runs on a single 5-volt power supply. In addition, clock speeds for current versions of the 68000 run from 4 MHz up to 12.5 MHz. The high clock frequency, together with the ability to load 16 bits of data at once (twice that of an 8-bit machine), greatly increase the processing speed beyond the barriers encountered in the 8-bit machines.

### 2.4 68000 DATA ORGANIZATION

Even though the 68000's data and address registers are 32 bits long, it is possible to work with smaller bit quantities. Many of the processor's instructions can be directed to operate on 16, 8, or even 1 bit at a time! We generally refer to 8-, 16-, and 32-bit data lengths as bytes, words, and long words. Telling an assembler what data type to use in an instruction is done by following the

instruction mnemonic with a .B, .W, or .L extension. For example, MOVE.B means to move a byte of data, and MOVE.L means to move a long word of data. When the 68000 is directed to use only 8 bits of a register, it will use the lower 8 bits (bits 0 through 7). Words occupy the lower 16 bits of the register. Operations on these lower bits do not affect the higher bits in the register.

Figure 2.2 shows how the 68000 stores 16-bit data types in memory. The upper eight bits of the word occupy a memory location that has an even address. The lower eight bits are stored in an odd memory location one higher than that of the upper byte. The figure indicates that the processor has stored the word value B52D in memory locations 0 and 1, with the next available word boundaries starting at addresses 2 and 4. The hardware signals  $\overline{\text{UDS}}$  and  $\overline{\text{LDS}}$  are used to indicate which portion of the data bus contains information:  $\overline{\text{UDS}}$  for bits 15–0 and  $\overline{\text{LDS}}$  for bits 7–0.

The 68000 is capable of detecting operations that may try to violate this storage technique (for example, trying to write a word to an odd location), resulting in another type of exception, called an **address error**. Long words are stored with the upper word occupying the first two memory locations and the lower word the next two locations. Bytes may be stored too, in any location, regardless of the even/odd requirement.

### 2.5 68000 INSTRUCTION TYPES

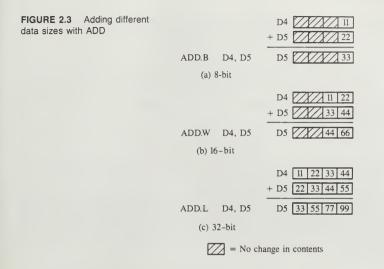

The 68000 contains several groups of instructions designed to make the task of writing source code less tedious for the programmer. Older machines often contained many different forms of instructions that all did the same thing. For example, 8- and 16-bit additions were handled by different instructions, requiring the use of different mnemonics in the source code. The 68000 eliminates the need for the programmer to keep track of these differences. A single ADD instruction mnemonic can be easily coded to perform 8-, 16-, and 32-bit additions on either data or address registers. The same is true for data transfer instructions) for data transfers, register to register, register to memory, and immediate to register/memory use only *one* mnemonic to handle everything. Figure 2.3 shows the three ADD instructions used to add 8-, 16-, or 32-bit portions of D4 to D5.

The different instruction groups may be classified as arithmetic (add, subtract, multiply, divide, clear, and complement), logical (AND, exclusive OR,

OR, shifting, and rotates), data transfer (register exchange, transfers from memory to register, register to memory, and immediate data transfers), branches (conditional, unconditional, and special looping instructions), and machine control (stack manipulation, bit testing, STOP, RESET, and some other special ones for use with exceptions).

Altogether there are over 50 different types of instructions. When we add the 14 different addressing modes—which we will cover next—and operations on different data types, we come up with a very flexible instruction set!

### 2.6 68000 ADDRESSING MODES

The 68000 contains 14 different addressing modes derived from 6 basic types. These types are register direct, absolute data, program counter relative, register indirect, immediate data, and implied. Some of these types support the use of address or data registers in forming the address, and the addition of an offset as well. When different combinations of address or data registers and offsets are used, we end up with 14 different possible addressing modes. All of the addressing modes that follow are covered in detail in the next chapter.

Register direct addressing uses the value in one of the address or data registers as the operand. An example would be:

MOVE.L D0,D3

which copies the contents of register D0 into register D3.

Absolute data addressing means that the operand address has been included in the instruction itself. The following is an example:

MOVE.B INIT, COUNT

where INIT and COUNT are reserved byte locations in memory.

Program counter relative addressing works by adding an offset value to the current program counter. This offset value may be stored in an index register. All address and data registers may be used as index registers. Examples of this addressing mode are:

| BRA    | NEXT          |

|--------|---------------|

| MOVE.W | DATA, D3      |

| MOVE.B | DATA(A5.L),D4 |

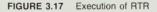

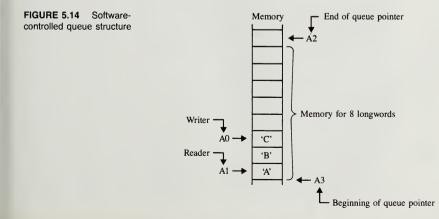

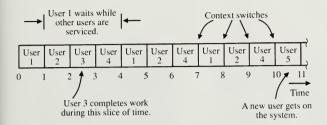

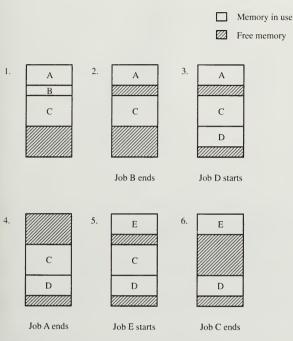

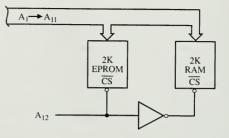

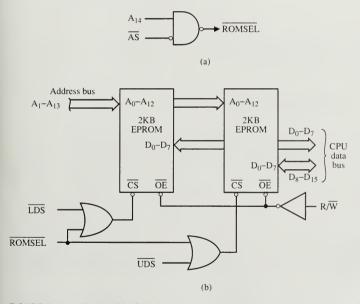

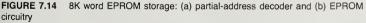

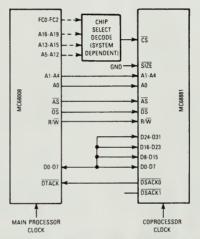

where A5 now acts as an index register, and DATA is the starting address of a data table located somewhere in memory.