# THE 68000 MICROPROCESSOR Andrew M.Veronis

Andrew M. Veronis, Ph.D. Professor Department of Electrical Engineering Howard University Washington, D.C.

Copyright ©1988 by Van Nostrand Reinhold Company Inc. Library of Congress Catalog Card Number 87-13297

All rights reserved. No part of this work covered by the copyright hereon may be reproduced or used in any form or by an means-graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems-without written permission of the publisher.

Van Nostrand Reinhold Company Inc. 115 Fifth Avenue New York, New York 10003

Van Nostrand Reinhold Company Limited Molly Millars Lane Wokingham, Berkshire RG11 2PY, England

Van Nostrand Reinhold 480 La Trobe Street Melbourne, Victoria 3000, Australia

Macmillan of Canada Division of Canada Publishing Corporation 164 Commander Boulevard Agincourt, Ontario M1S 3C7, Canada

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

#### Library of Congress Cataloging-in-Publication Data

Veronis, Andrew. The 68000 microprocessor.

Includes index. 1. Motorola 68000 (Microprocessor) I. Title. QA76.8.M672V47 1988 004.165 87-13297

ISBN-13: 978-1-4684-6649-2 DOI: 10.1007/978-1-4684-6647-8 e-ISBN-13: 978-1-4684-6647-8

This book is dedicated to my dear mother-in-law Eleanor Hough Buckler, for all the love and kindness she has shown me.

### Preface

The Motorola MC68000 family of microprocessors is undoubtedly a revolutionary set of devices. The MC68000 is the first advanced 16-bit microprocessor with a 32-bit internal architecture and the first with 16-megabyte, nonsegmented, direct memory addressing. The processor's six basic addressing modes are equivalent to 14, when one considers all of the variations among these modes. Combined with the device's data and instruction types, the modes provide more than 1000 useful instructions.

The book you are about to study has been developed as an aid to the hardware designer and as a supplement to the Motorola seminars on the 68000 microprocessor. The text includes a detailed description of the MC68000 and two complete systems that show how this processor can be interfaced to the outside world.

The book follows a "top-down" approach. A brief history of microprocessors is provided first. Chapter 2 details the MC68000 by describing its registers, control lines, and capabilities.

Chapter 3 introduces a small MC68000-based system. Although this system is characterized in the book as hypothetical, it is indeed the Educational Computer Board, used in the various Motorola seminars.

The addressing modes and instructions are explained in Chapter 4, which includes helpful hints on how instructions can be used. Chapter 5 provides an in-depth description of additional instructions and numerous examples.

Chapter 6 discusses exception handling and interrupts.

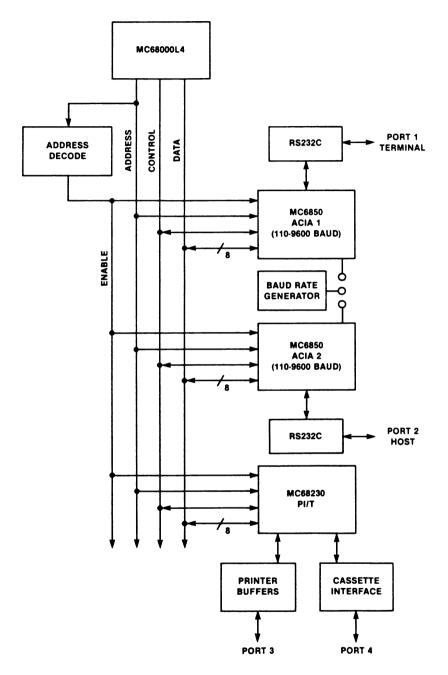

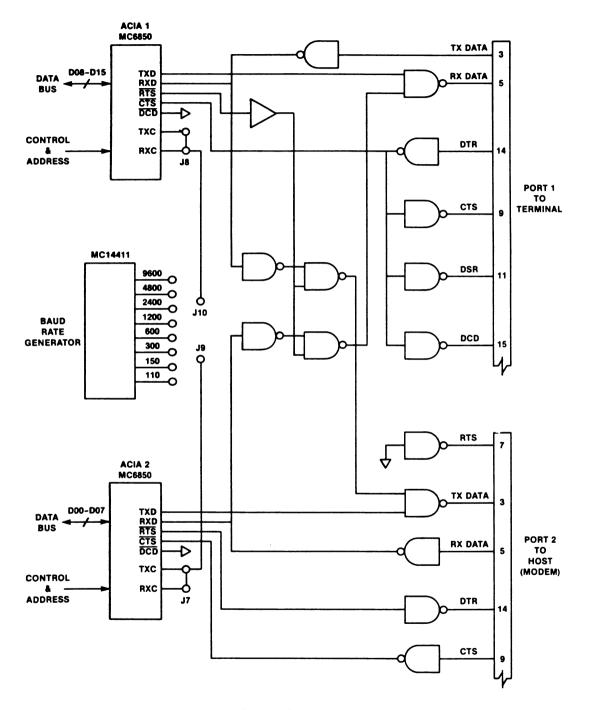

Chapter 7 describes how the MC68000 processor can be connected to eightbit and 16-bit peripheral devices. This Chapter also covers the interfacing of the Motorola Educational Computer Board to a terminal, a modem, a printer, and a cassette interface. Various interfacing programs are listed in this Chapter.

Chapter 8 provides full description of a second MC68000-based system, the VU68K. This system was built initially by students of the Computer Science Department of Vanderbilt University, and subsequently has been constructed by some of the author's students. The most interesting part of this Chapter is the detailed description of an operating system monitor, the VUBUG. Study of the VUBUG provides the reader with valuable experience in the use of the MC68000 instructions, as well as in the design of a basic, but fully functional, operating system monitor.

The writing and production of a book really involves many people, such as reviewers, copy editors, and artists. Perhaps the only chance that an author has to thank these people is through the preface of the book. I wish to thank everyone who participated in the production of this book. I particularly wish to thank my friend Joe Gordon for helping me with the illustrations.

Most authors use the preface of their book to thank their loved ones for their patience. I wish to do the same, to thank my dear wife Elizabeth Veronis not only for her tremendous patience but also for her active participation in the typing and editing of the manuscript. Her help has been invaluable.

Appendices B and D are the copyrighted property of Motorola Semiconductors, Inc. and are included in this book by written permission.

> Andrew M. Veronis Annapolis, Maryland

### Contents

Preface vii

#### Chapter 1. BASIC CONCEPTS 1

BRIEF HISTORY OF MICROPROCESSORS 1 DESIGN OF A MICROPROCESSOR 2 Design Considerations 2 Registers 3 Addressing Modes 3 Prefetch 4 Multiple Arithmetic-Logic Unit 5 Microprogramming 5 Peripheral Devices 5

DATA REPRESENTATION 6 Terminology 6 Data Types 6

Chapter 2. INTRODUCTION TO THE MC68000 9

GENERAL LAYOUT 9 DATA BUS 10 ADDRESS BUS 10 ASYNCHRONOUS BUS CONTROL 10 FUNCTION CONTROL 13 SYNCHRONOUS BUS CONTROL 14 SYSTEM CONTROL 15 DIRECT MEMORY ACCESS CONTROL 15 INTERRUPT CONTROL 16 REGISTERS 17 Data Registers 17 Address Registers 17 Program Counter 17 Status Register 17

Chapter 3. A SMALL MC68000 SYSTEM 19

INTRODUCTION BLOCK DIAGRAM AND MEMORY MAP Block Diagram Memory Map

BUSES 22 ADDRESS MULTIPLEXING 22 **RESET/HALT AND SYSTEM CLOCK 23** Reset/Halt Circuit 23 System Clock 28 TIMING 28 BUS TIMEOUT LOGIC 34 **DESIGN OF RAM AND ROM INTERFACE 34** ROM Circuit 34 RAM Circuit 35 Chapter 4. ADDRESSING MODES; INSTRUCTION SET 42 ADDRESSING MODES 42 Memory Accessing Rules 42 Effective Address and Extension Word 42 Register Direct Modes 45 General 45 Data Register Direct 45 Address Register Direct 47 Memory Address Modes 47 General 47 Address Register Indirect 47 Address Register Indirect with Postincrement 48 Address Register Indirect with Predecrement 49 Address Register Indirect with Displacement 49 Address Register Indirect with Index and Displacement 50 Special Address Modes 51 Absolute Short 51 Absolute Long 51 Immediate Mode 51 Program Control Modes 52 General 52 Program Counter with Displacement 52 Program Counter with Index 52 Inherent Mode 52 Summary 52

#### **INSTRUCTIONS 53**

Chapter 5. INSTRUCTION SET – A MORE INTENSIVE EVALUATION 54

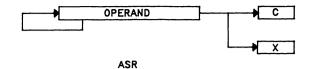

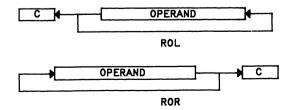

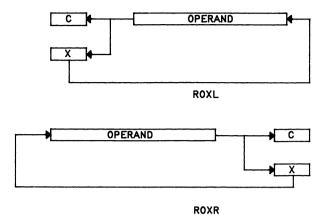

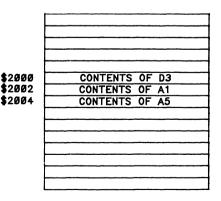

DATA MANIPULATION INSTRUCTIONS 54 Arithmetic Operations 54 Logical and Shifting Instructions 60 Logical Instructions 60 Shifting Instructions 63 Bit Manipulation Instructions 65 DATA MOVEMENT INSTRUCTIONS 66 PROGRAM CONTROL INSTRUCTIONS 69 Unconditional Branch 69 Conditional Branch 69 POSITION INDEPENDENCE INSTRUCTIONS 70 HIGH-LEVEL LANGUAGE AIDS 70 PROGRAMMING HINTS 73

Chapter 6. EXCEPTION HANDLING 76

GENERAL 76 INTERRUPTS 83

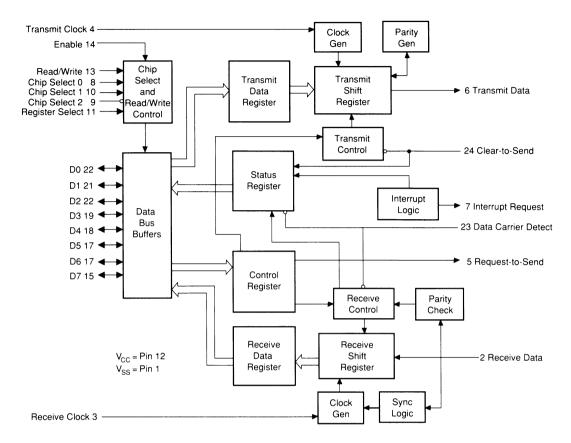

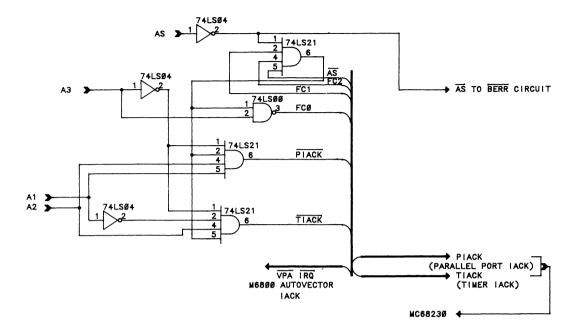

Chapter 7. PERIPHERAL DEVICES 92

INTRODUCTION 92 MEMORY MAPPING OF I/O SPACE 92 MC6850 ACIA 92 MEMORY MAPPING OF ACIA 97 GENERATING INTERRUPT REQUEST SIGNALS 97 PARALLEL INTERFACE/TIMER 104 DESIGNING THE PRINTER INTERFACE 106 PROGRAMMING THE INTERFACE 108 DESIGN OF THE CASSETTE INTERFACE 110

#### Chapter 8. ANOTHER 68000-BASED SYSTEM 114

HARDWARE DESCRIPTION 114 THE OPERATING SYSTEM MONITOR 118 MONITOR COMMANDS 119 The "b" Command: Set/Remove Breakpoints 120 The "c" Command: Copy Memory Blocks 120 The "d" Command: Display Data to Terminal 120 The "e" Command: Enter Terminal Emulator Mode 120 The "g" Command: Execute a User Program 121 The "g" Command: Load Program from Host (S-format) 121 The "n" Command: Examine/Modify Memory 121 The "p" Command: Load/Execute a Prototype Command 122 The "r" Command: Examine/Modify Registers 122 The "s" Command: Single-Step Mode 122 The "t" Command: Trace Program Execution 123

TRAPS **123** EXCEPTION PROCESSING **124** THE MONITOR **124**

Appendix A. S-RECORD OUTPUT FORMAT 153

Appendix B. INSTRUCTION SET DETAILS 159

- Appendix C. INSTRUCTION FORMAT SUMMARY 271

- Appendix D. MC68000 INSTRUCTION EXECUTION TIMES 293

- Appendix E. MC68000 INSTRUCTION EXECUTION TIMES 301

Index 313

### Chapter 1 Basic Concepts

#### **BRIEF HISTORY OF MICROPROCESSORS**

The first two microprocessors—the 4004 (a four-bit set of devices) and the 8008 (an eight-bit device on a single chip)—were produced in the early 1970s by a newly formed company, Intel Corporation. The 4004, also known as the MCS-4, was designed to replace six custom chips in a desktop calculator and was therefore programmed for serial, binary-coded, decimal arithmetic (a very common practice in handheld and desktop calculators). Although the client, a Japanese manufacturer named Busicomp, went out of business before it could put the 4004 to work, this set of devices was soon adapted for numerous other applications.

A U.S. company named Computer Terminal Corporation (also known as Datapoint) similarly requested Intel to design a push-down stack chip for a processor to be used in a CRT terminal. Datapoint intended to build a bit-serial processor in TTL logic with a shift-register memory – a design that would require a fair number of devices. Intel suggested that the entire design could be implemented in one chip. This new processor was the 8008. Although Datapoint eventually did not use the chip because of the long lead time Intel required, the device was quickly adopted by other logic design engineers, who saw the advantages to be derived from microprocessors.

At about the same time, Motorola, Texas Instruments, Zilog, and other semiconductor manufacturers were gearing up to capture a share of what was to become the largest semiconductor market. Improved devices such as the Intel 8080 (second-sourced by other manufacturers, including Texas Instruments and National Semiconductors), the Zilog Z80 (the most popular eight-bit processor ever marketed), and the Motorola 6800 (also an extremely popular eight-bit microprocessor) have dominated the market for more than a decade.

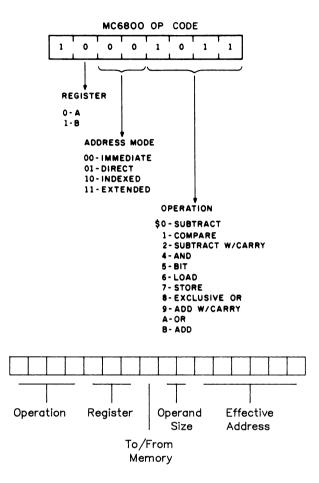

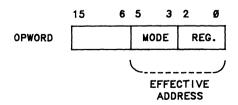

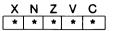

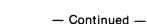

As the benefits of microprocessors became more apparent, design engineers and, more particularly, programmers increasingly demanded better performance. Eight-bit microprocessors are designed to replace logic circuits and, consequently, emphasize controller-type capabilities rather than ease-of-programming elegance. Compare, for example, the instruction format of an eight-bit processor to that of a 16-bit device, as shown in Fig. 1-1.

Clearly, an eight-bit processor lags behind in the available number of registers, instructions, and addressing modes, as well as the memory addressing range. All

Fig. 1-1. Formats of 8-bit and 16-bit instructions.

of these features are needed for efficient programming. Thus, eight-bit processors gradually are giving way to 16-bit and 32-bit processors.

#### **DESIGN OF A MICROPROCESSOR**

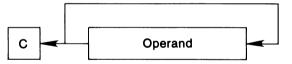

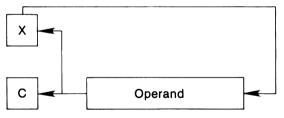

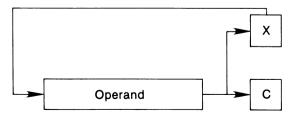

#### **Design Considerations**

Numerous factors affect the overall performance of a microprocessor system, including internal organization, speed, instruction set, addressing modes, memoryhandling capacity, interfacing ease, and availability of compatible peripheral devices. The system designer must consider them all.

Some of these factors will be described in the following pages. To facilitate this description, a powerful 16-bit processor—the Motorola MC68000—will be referred to from time to time. This device will not be examined in detail, however, until Chap. 2.

#### Registers

One significant advantage of a 16-bit microprocessor over an eight-bit device is that the former has twice the word width; as a result, a 16-bit device can handle twice as much information, thus increasing the processing speed of a system. Another advantage is the increased number of internal registers this device provides the programmer. The MC68000 excels in both of these areas.

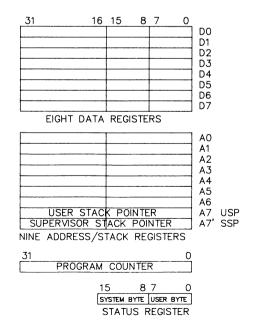

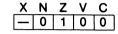

As shown in Fig. 1-2, the Motorola MC68000 has eight 32-bit data registers, nine 32-bit address registers (registers A7 and A7' are the user and supervisor stack pointers), and a 32-bit program counter (although the maximum address range is 24 bits). Since most of its data and address registers are undedicated, the MC68000 thus provides greater flexibility.

#### **Addressing Modes**

Having a good number of addressing modes is likewise an advantage for a microprocessor. The MC68000 has 15 addressing modes. With few exceptions, each instruction operates on bytes, words (16 bits), and longwords (32 bits), and most instructions can use all 15 modes.

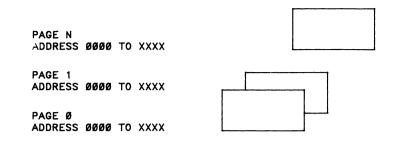

One weakness of an eight-bit microprocessor is its limited memory-accessing capacity. With a 16-bit address bus, this device can directly address only 65,536 addresses. Some schemes increase the address range of an eight-bit processor, or so it seems. For example, Fig. 1-3 illustrates a method called *paging*. In this scheme, the total memory area is divided into pages. Although the 16-bit address range remains unaltered, bits in another register, such as the program counter, are used to designate the number of the page. Theoretically, this practice

Fig. 1-2. MC68000 registers.

Fig. 1-3. Memory paging.

increases memory capacity, but it is dependent on the bits allocated to designate page numbers. Although the addition of several page registers will eliminate the problem of page bits, paging is still limited by the fact that only a single page can be accessed at a time. This method is tricky, moreover, and time-consuming.

To overcome the deficiencies of paging, some 16-bit microprocessors use a method called *memory segmentation*. Since the memory spectrum is divided into segments, this method is similar to paging, as Fig. 1-4 shows. A segment number added to the 16-bit address identifies each segment. Segmentation allows some possibility of address relocation, but the size of each segment is a limiting factor (it cannot exceed 64 kilobytes), and the desired segment must be loaded as well.

The most straightforward method of memory accessing is called *linear accessing.* Simply speaking, a processor with linear addressing capabilities has adequate address lines to access memory directly. For example, the 23 external address lines of the MC68000 allow direct access of 8.4 million words of memory. Since programmers are always hungry for more memory, however, provisions have been made to carry out a type of paging with some control lines furnished by the MC68000. This method will be explained later. Furthermore, memory management devices can be used with the MC68000 to provide additional memory capacity.

#### Prefetch

A significant factor in the selection of a microprocessor is the manner in which a particular device fetches instructions from memory. After an eight-bit microprocessor fetches an instruction, the address- and data-fetching circuits and buses of

Fig. 1-4. Memory segmentation.

the device remain idle while the instruction is being executed. Needless to say, this represents a loss of time. The MC68000, in contrast, has a *prefetch queue*. During the execution of one instruction, the device fetches a number of other instructions and aligns them in the prefetch queue. Consequently, the microprocessor nearly always has an instruction available for processing. This instruction is stored in close proximity to the arithmetic-logic unit (ALU).

#### **Multiple Arithmetic-Logic Unit**

A system designer also must consider features that will increase the processing speed of a microprocessor. All eight-bit microprocessors feature only a single arithmetic-logic unit, and this is used both for data processing and for calculation of addresses. In a processor that uses indexed addressing, the offset value must be added to an address via this single ALU at a time when data could otherwise be processed.

In contrast, the MC68000 uses not only a 16-bit-wide ALU as the main dataprocessing mechanism but also two other 16-bit ALU to function in parallel as a 32-bit ALU for the calculation of addresses. Thus, at the same time a 16-bit datum is being processed, the address ALU can be calculating an effective address (this term will be described later). The 16-bit data ALU also is used to process 32-bit values by taking two passes at 16-bit data, one for the lower word and one for the upper.

#### Microprogramming

All eight-bit and most 16- and 32-bit microprocessors are designed as **hardwired logic** units – i.e., the control unit is built of logic gates permanently wired to each other. This design eliminates excessive use of components and improves speed on the one hand, but, on the other, not only reduces the flexibility of the control unit but also overcomplicates the design of a complex unit.

Microprogramming of a complex control unit simplifies design by making the unit modular; that is, each section of the unit may be modeled, built, and tested independently. Additionally, a microprogrammed design permits a customer to make design changes (although the MC68000 uses a microprogrammed design, Motorola is rather reluctant to implement a customer's microcode into this design).

#### **Peripheral Devices**

To compete successfully, a manufacturer embarking on the design of a microprocessor must provide an entire family of peripheral devices. Design and production of such devices are frequently very expensive and time-consuming. Concerned with the possible loss of their share of the microprocessor market, several manufacturers have introduced microprocessors without peripheral devices. Motorola chose to add several control lines to the MC68000 to make it directly compatible with the readily available peripheral devices from the MC6800 family. This

approach afforded Motorola ample time to develop 16-bit peripheral devices and also gave customers the benefit of using low-priced eight-bit peripheral devices.

#### DATA REPRESENTATION

#### Terminology

The smallest unit of data stored in the memory of a computer is called a *bit*, an abbreviation of the words "binary digit." A bit has the value of zero (0) or one (1).

Bits are combined to make *nibbles* (four bits, useful for representing one binarycoded decimal digit (the equivalent of decimal zero to nine)) and *bytes* (eight bits). A byte may denote a single character (usually encoded in ASCII), a number from 0 to 255, or two BCD numbers (0 to 99).

The term *word* varies among computers. In all cases, a word is made up of bytes. In 16-bit computers, a word consists of two bytes; in 32-bit computers, a word consists of four bytes; and so on. Simply defined, a word is the maximum length of information that the data bus of a computer can transfer. The memory area of a computer usually has the length of the computer's word; that is, a computer is equipped with a memory 8 bits wide, 16 bits wide, etc.

A collection of words ordinarily is called a *block*.

All of these terms refer to units of storage inside a computer or memory. Distinctions must be made, however, between what various strings of bits indicate, since they may signify a character or a positive number or a false/true condition. In other words, data must be identified by "type."

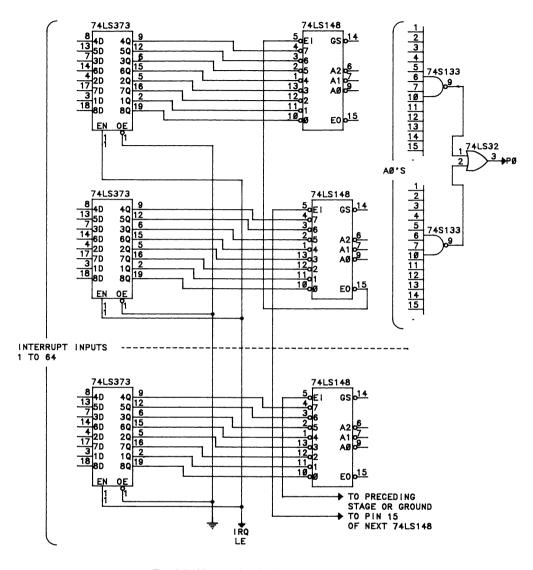

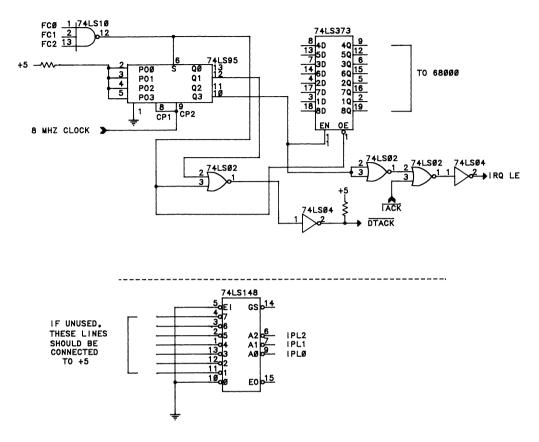

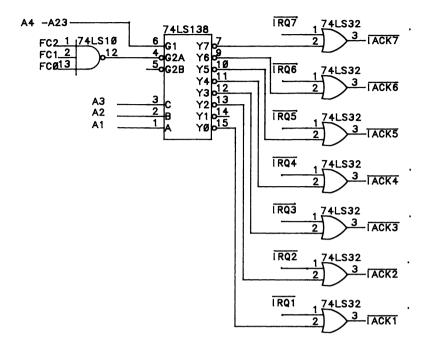

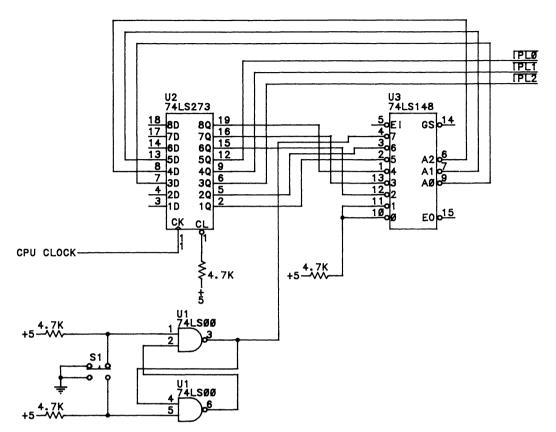

#### **Data Types**

A bit is used to denote a "logical" state of "true" or "false." In this sense, the logical bit is called a *flag* and is used for comparison of two values, for branching, or for other purposes. Thus, single bits are "logical data types."

Inside a computer, a number may be represented in various ways. The number can be, for instance, an unsigned number, starting from zero, called an *ordinal*. For example, in eight-bit microprocessors, an ordinal number can be any number from 0 to 255 (00000000 to 11111111); as the data-bus width of a microprocessor increases, so does the representation of ordinal numbers.

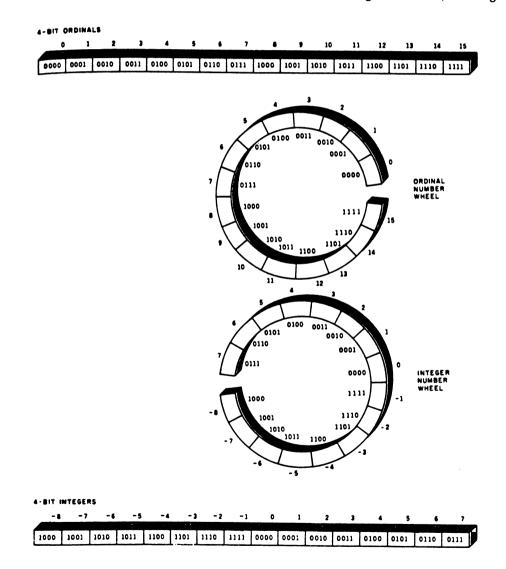

A whole number, whether positive or negative, is called an *integer*. In all microprocessors, integers are represented in *two's complement form;* that is, the leftmost bit of an integer constitutes both the maximum value of the integer and its sign (0, for positive; 1, for negative). Various clever methods have been devised to represent numbers in two's complement form easily.

One method is shown by Dr. Christopher Morgan and Mr. Mitchell Waite in their book entitled 8086/8088 16-bit Microprocessor Primer. Ordinal numbers from 0 to  $2n^{-1}$  can be shown around a wheel, as in Fig. 1-5, so that the last number is before the first. If the wheel is separated halfway around and negative

integers are assigned to positions on the separated wheel – counting backwards from zero – the two's complement representation is derived. The wheel must be separated precisely at the point where the most significant bit (*msb*), or leftmost digit, changes sign; that is, all nonnegative numbers have a 0 as their msb, and all negative numbers have a 1 as their msb. This bit is called the *sign bit*. Thus, in 16-bit computers, integers ranging from -32,768 to +32,767 are represented; in 32-bit computers, numbers from -2,147,483,648 to +2,147,483,647 are represented.

Characters are depicted inside computers by various codes. The most frequently used code is the eight-bit ASCII (it is now an eight-bit code). An eight-

Fig. 1-5. Ordinal number representation.

bit number represents the characters of the alphabet (A through Z), numerals (0 through 9), and special characters. Most microprocessors use a subset of this eight-bit ASCII code. If, for example, a six-bit ASCII code is used, then lower-case letters cannot be represented.

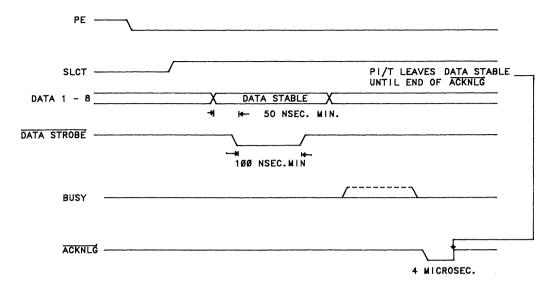

A series of characters is called a *string*. In programming languages, strings are used to display a message.

Decimal numbers are denoted inside a computer in *Binary-Coded Decimal* notation (BCD). Each decimal digit, from 0 through 9, is represented by a four-bit number.

The preceding survey provides an overview of data types but is by no means complete. The reader is encouraged to study the topic of number systems in other specialized texts.

# Chapter 2 Introduction to the MC68000

#### **GENERAL LAYOUT**

The MC68000 is a bulky integrated circuit that is 1.2 inches longer and 0.4 inches wider than a 40-pin package. The fact that it is equipped with numerous pins, however, makes it easier to interface.

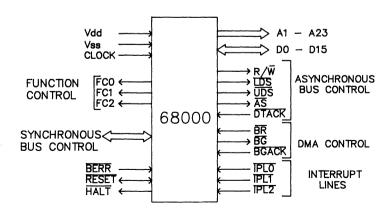

As Fig. 2-1 shows, the MC68000 has 64 external pins that function within one of the following groups (the numbers in parentheses denote the number of pins allocated to each function):

Power supply (4) Clock (1) Address Bus (23) Data Bus (16) Function Control (3) Synchronous Bus Control (3) System Control (3) Asynchronous Bus Control (5) Direct Memory Access Control (3) Interrupt Control (3)

Fig. 2-1. Pin configuration of MC68000.

The orientation of the arrows shows whether a group is bidirectional or unidirectional. Each signal associated with these categories is described in this chapter. The verbs "assert" and "negate" are used throughout this text solely to dispel any doubts about the electrical status of a signal. Regardless of actual voltage level, "asserted" indicates an active signal and "negated," an inactive signal.

#### DATA BUS

In the MC68000, the 16 lines of the data bus are, as in any other microprocessor, bidirectional. Their function is straightforward, requiring no further description.

#### ADDRESS BUS

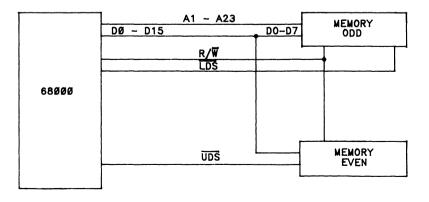

Although the MC68000 displays 23 address lines, the device is actually equipped with 24. Address A0 is encoded internally with the length of the operand to form the *Upper Data Strobe* (UDS) and *Lower Data Strobe* (LDS) signals. With 24 effective address lines, the total address space can be computed as 16,777,216 physical locations. Since the MC68000 memory space is organized as 16-bit words, however, the total number of physical locations is reduced to 8,388,608 words.

The address bus takes up the largest number of pins because Motorola does not use bus multiplexing (a feature that saves pins but requires the use of external latches for demultiplexing).

#### ASYNCHRONOUS BUS CONTROL

Although the address bus is not multiplexed, the MC68000 has an *Address Strobe*  $(\overline{AS})$ . Frequently, this signal can be negated by connection to a positive power supply via a pull-up resistor. There are, however, peripheral devices that function properly when  $\overline{AS}$  is used to assert them.

The  $\overline{AS}$  signal defines the time interval during which the address lines (A1 to A23) and the function code lines (FC0 to FC2) are valid. When a MC68000based system uses dynamic memory, it is the  $\overline{AS}$  signal that notifies the memory controller of the beginning of a cycle. The same signal also provides the lock-out mechanism for read–modify–write cycles during a Test-and-Set (TAS) instruction.

The MC68000 has the capability of dividing its memory range into eight-bit sections.\* The UDS and the LDS delineate the time during which data are transferred over the data bus. When either (or both) of these signals is asserted, the Read/Write ( $R/\overline{W}$ ) line also is asserted, and the address on the address bus is valid.

<sup>\*</sup>This includes peripheral devices, since the MC68000 uses memory-mapped input/output (I/O) devices.

The UDS and LDS are used to permit byte operands as well as word and longword data. Both signals are asserted for word transfers. For byte transfers, UDS is asserted only on an even address (D8 to D15) and LDS only on an odd address (D0 to D7). Thus, to move byte data, all devices on the upper half of the data bus must be strobed with UDS and all devices on the lower half with LDS.

The R/W line dictates the direction of data transfer. This single line is timed so that it can control the direction of data-bus buffers on multiprocessor systems. Since this single line accomplishes the functions of both read and write (a feature inherited from MC6800 devices), it is worth noting that data are read when the line is active-high and written when the line is active-low. Once an address is valid during a write cycle, placing the R/W line low and combining it with an active strobe enable the transfer of data to static memories.

The MC68000 must be notified of the termination of a bus cycle. There are three ways by which a bus cycle is terminated. One of them belongs to the asynchronous bus control group, and the other two will be discussed later. The normal termination signal to the MC68000 is the Data Acknowledge line (DTACK), which informs the processor that the data to be processed are valid on the data bus. Since this line is one of the most significant inputs to the device, a designer must be careful about how and when DTACK is supplied. If a DTACK signal is not received, the MC68000 will remain idle indefinitely, waiting all the while for the DTACK to indicate that data are available. The DTACK and several other signals will be described at greater length in Chap. 3.

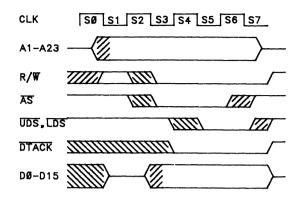

Now that all of the asynchronous bus control signals have been identified, it is appropriate to examine the timing diagram of a read cycle, as shown in Fig. 2-2, and of a write cycle, as shown in Fig. 2-3. An interesting point, shown in both diagrams, is that the  $R/\overline{W}$  line, whether on initiation of a read or a write cycle, is always asserted in the read mode. This safety feature eliminates the possibility of accidental destruction of data in memory.

Let us examine the read cycle first. At the leading edge of S2, the  $\overline{AS}$ ,  $\overline{LDS}$ , and  $\overline{UDS}$  lines are all asserted until the trailing edge of S6, when data are latched onto the data bus, and  $\overline{DTACK}$  has been asserted. In other words, in the asynchronous bus mode, the MC68000 initiates a read or write cycle by asserting the address strobe and waiting for a  $\overline{DTACK}$  before assuming that data on the bus are valid. If the MC68000 does not receive a  $\overline{DTACK}$  at the trailing edge of S4, the device

| CLK        | SØ S1 S2 S3 S4 S5 | S6 S7 |

|------------|-------------------|-------|

| A1-A23     |                   |       |

| <b>R/₩</b> |                   |       |

| AS, LDS,   |                   | [777] |

| DTACK      |                   |       |

Fig. 2-2. Read cycle of MC68000.

Fig. 2-3. Write cycle of MC68000.

enters S5 and S6 and performs an internal synchronization process. Then, the MC68000 introduces wait states and remains in this condition until the DTACK is received.

Delay in the arrival of DTACK, mind you, may be either intentional or unintentional. It is the latter that should be of more concern to a system user. For example, an intentional DTACK delay may be generated for devices that require additional access time (because of slow memories or peripherals). In this case, a shift register or delay line is used, to allow cycles to be lengthened in one-clock-cycle increments. Thus, the asynchronous action of DTACK allows the construction of systems with variable cycles, from 500 nsec @ 8MHz all the way up to the maximum delay required.

The write cycle presents several variations in timing. The  $\overline{\text{LDS}}$  and  $\overline{\text{UDS}}$  assertion takes place in S4 rather than simultaneously with  $\overline{\text{AS}}$ . The R/ $\overline{\text{W}}$  line changes to the write mode in S2, when  $\overline{\text{AS}}$  is asserted.

Figure 2-4 shows a minimum configuration of an MC68000-based system with all of the asynchronous bus signals, excluding  $\overline{AS}$ , in place. The system is designed for byte addressing, as explained earlier.

Fig. 2-4. Minimum configuration of MC68000 system.

| STATE                 | MODE       | FC2 | FC1 | FC0 |

|-----------------------|------------|-----|-----|-----|

| Reserved – Motorola   | User       | 0   | 0   | 0   |

| Data space            | User       | 0   | 0   | 1   |

| Program space         | User       | 0   | 1   | 0   |

| Reserved – user       | User       | 0   | 1   | 1   |

| Reserved – Motorola   | Supervisor | 1   | 0   | 0   |

| Data space            | Supervisor | 1   | 0   | 1   |

| Program space         | Supervisor | 1   | 1   | 0   |

| Interrupt Acknowledge | Supervisor | 1   | 1   | 1   |

Table 2-1. Status of Function Lines.

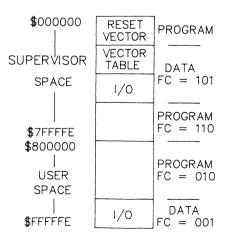

#### **FUNCTION CONTROL**

Three lines (FC0 to FC2) indicate the state of the processor. The MC68000 can be in one of two modes—the user or the supervisor mode. Table 2-1 provides a summary of the processor state as indicated by the function code lines. In this table, FC2 indicates whether the MC68000 is in the user or supervisor mode. Assertion of all three lines indicates that the MC68000 has acknowledged an interrupt. Table 2-1 may be put into practice\_by the use of a 74LS138 decoder, as Fig. 2-5 shows.

The function lines are decoded to separate memory into four sections. Data memory is defined as the area that contains variables, vectors, stacks, queues, strings, tables, lists, or any other type of data found separate from the instructions, and fixed operands, which are found with the instructions that use the operands. The watchdog timer circuit, discussed in Chap. 3, signals a bus error if a DTACK is not asserted on time (about 10 microseconds). Such an error may be caused by the failure of a memory access to remain within the allocated memory space. As described later, the function control lines can also be used for further expansion of the memory capacity of the MC68000.

Fig. 2-5. Decoding of function lines.

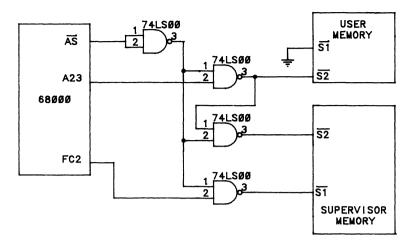

Fig. 2-6. Use of function line FC2 to distinguish between supervisor and user memory areas.

Since line FC2 indicates at all times whether the MC68000 is in user or supervisor mode, this line can be effectively used, with simple gating, to prevent accidental access of supervisor memory by a user. Figure 2-6 shows just such a scheme. When both the  $\overline{AS}$  and FC2 lines are asserted, the inputs to the NAND gate are high; thus, the NAND gate asserts the S1 chip select of the supervisor memory. When an address in the user area is accessed, the NAND gate asserting the user S2 prevents the access of the supervisor S2.

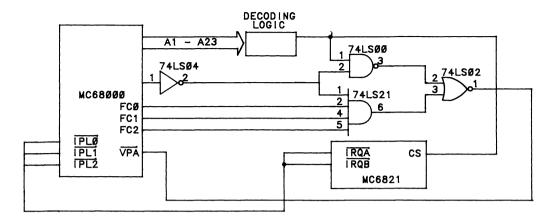

#### SYNCHRONOUS BUS CONTROL

The three synchronous bus control signals are used to interface the MC68000 with MC6800 peripheral devices. The *Enable* signal (E) is the phase-two clock that the latter require and that defines the periods of data to and from the processor. The second signal, the *Valid Memory Address* (VMA), is used in the chip-select circuitry of a MC68000 system using MC6800 peripheral devices. During reference to a peripheral, VMA meets all timing requirements for a chip-select input. The VMA signals on both the MC6800 and the MC68000 are identical in function but opposite in voltage levels; the MC6800 VMA is active–high, whereas the MC68000 VMA is active–low. The reason for this difference is that the MC68000 VMA prevents accidental addressing of peripherals when the bus is three-stated.

The third synchronous bus signal, called the *Valid Peripheral Address (VPA)*, is one of the signals that can be used to terminate a bus cycle. For each system application of the MC68000, bus cycles are likely to have different durations. Thus, if a constant-frequency clock is used to drive the Enable signal (E) on the peripherals, there must be a guarantee that data are transferred with respect to the clock, a requirement not often met in asynchronous-bus systems. The VPA line on the MC68000, however, accomplishes this task easily. When a peripheral address is decoded, the VPA signal, rather than  $\overline{\text{DTACK}}$ , is asserted. This approach notifies the processor to become compatible with the MC6800 family by waiting for the proper phase of E and then asserting  $\overline{\text{VMA}}$ . At this point, the address lines and  $R/\overline{W}$  signal are already valid. If the sequence begins too late during the E phase, all address and control signals remain stable until the next cycle, when compatible transfer can be ensured.

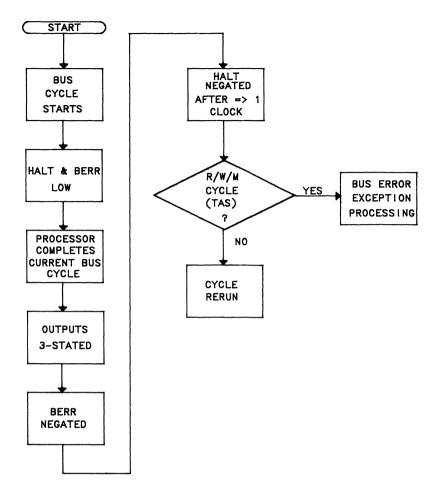

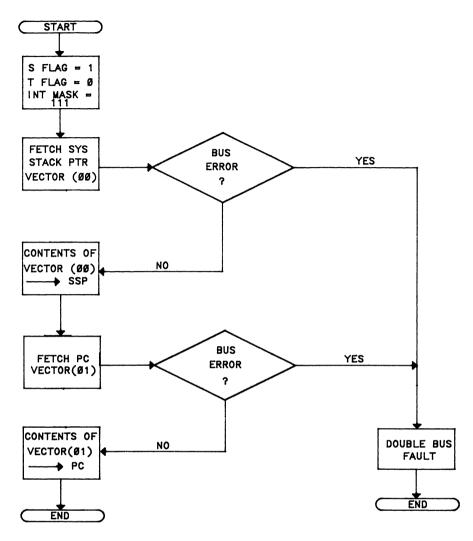

#### SYSTEM CONTROL

The third signal used to terminate a bus cycle is part of the three lines that comprise the system control group. The *Bus Error line* ( $\overline{\text{BERR}}$ ) terminates a bus cycle in the MC68000 system whenever an abnormal condition is sensed. This line operates in conjunction with the *Halt* ( $\overline{\text{HLT}}$ ) line, which also belongs to the system control group. When both  $\overline{\text{BERR}}$  and  $\overline{\text{HLT}}$  are asserted, a bus error is signaled, and the processor enters a rerun cycle.

The flowchart in Fig. 2-7 shows the steps that the MC68000 takes during a rerun cycle. Whenever the BERR and HLT lines are asserted (both active–low) during the initiation of a bus cycle, the processor completes the cycle and asserts its three-state outputs, thus preventing any information from reaching the buses. Shortly thereafter, the BERR line is negated, and, after a period of more than one clock cycle, the HLT line is also negated. At this point, the processor must determine whether a read–modify–write cycle is in progress for a Test-And-Set instruction. If so, the processor enters a bus exception-processing routine; that is, a rerun cycle routine is not executed. If a TAS instruction is not present, the MC68000 reruns the cycle during which the bus error line was asserted.

The HLT line also may be used in conjunction with the third line of the system control group—the RESET line. The MC68000 can be reset in two ways—i.e., during power-on or by a manual switch. The MC68000 also has a RESET instruction, which asserts the reset line and causes the reset of all external devices connected to the processor's reset line. During the execution of this instruction, the state of the processor, other than the program counter, is unaffected, and execution continues with the next instruction.

When the RESET and HLT lines are asserted simultaneously, either a power-on or a manual switch reset occurs. When the HLT line alone is asserted, however, a double bus fault occurs, and the processor must be reset to recover from this fatal error.

#### DIRECT MEMORY ACCESS CONTROL

The three lines in the direct memory access (DMA) control group are the *Bus Request* ( $\overline{BR}$ ), which the DMA controller provides to the processor, the *Bus Grant* ( $\overline{BG}$ ), which the processor sends to the controller, and the *Bus Grant Acknowledge* ( $\overline{BGACK}$ ), which the controller sends to the processor.

Fig. 2-7. Rerun cycle of MC68000.

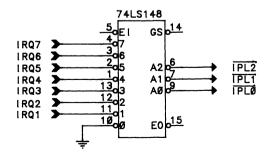

#### **INTERRUPT CONTROL**

The interrupt control is the last of the control line groups. This control consists of lines IPLO to IPL2 (Interrupt Priority Lines). Although interrupts will be described in detail in a later section, it would be of benefit to say a few words about the MC68000 interrupt system.

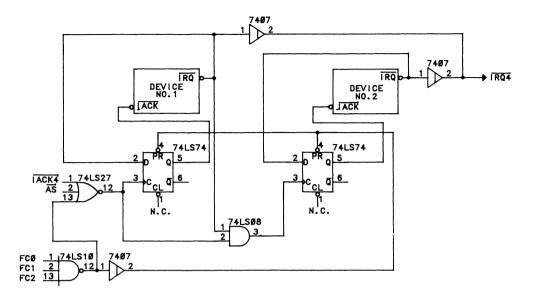

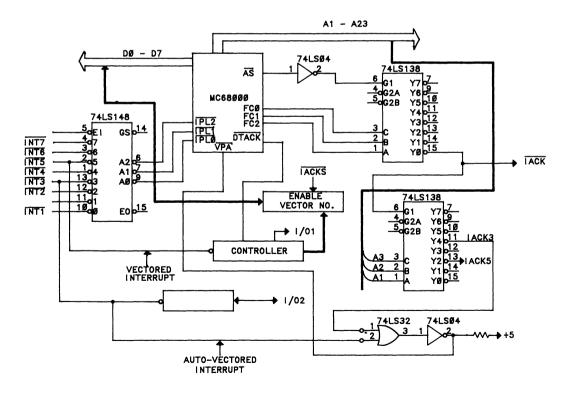

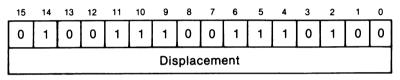

The MC68000 is capable of handling both vectored and autovectored interrupts. In a vectored interrupt system, the interrupting device transmits a vector number, which, multiplied by four, provides an interrupt routine address in a table of interrupts residing in memory. Some devices, including most MC6800 devices, however, cannot provide a vector number and must be autovectored. In an autovectored interrupt system, the processor examines the priority status of an interrupt to determine which vector number should be used. The interrupting device generates an interrupt request by asserting the IPL lines.

When a peripheral device is recognized as an autovector device by asserting  $\overline{VPA}$  instead of  $\overline{DTACK}$ , the processor translates the interrupt priority into one of eight locations in the vector table, fetches the vector, and branches to the interrupt service routine. Other signals are also involved during the autovector process, but this involvement will be explained later.

#### REGISTERS

The number of registers in the MC68000 already has been discussed. The reader must become familiar, however, with the idiosyncracies that some registers display.

#### **Data Registers**

Any data register in the MC68000 may be used for handling byte, word, or longword operand. The length of the operand to be handled is stated in an instruction. None of the MC68000 data registers is dedicated to a specific task; that is, any data register may be used as an index register, a temporary storage area for an operand, or an accumulator.

#### **Address Registers**

The nine address registers are restricted slightly in the size of operand that the registers may contain; they can contain only a word or longword. Furthermore, although any of the address registers may be used as user "stack pointers," two registers -A7 and A7 — are dedicated as stack pointers.

At the supervisor level, the operating system program can use both the supervisor stack pointer and the user stack pointer. Consequently, the user stack location can be changed in the course of switching from task to task.

#### **Program Counter**

The program counter is 32 bits long, but only 24 bits are used for effective addressing. This counter functions as it would in any other digital computer having the same organization; that is, the program counter always is automatically incremented to point to the next instruction to be executed.

#### Status Register

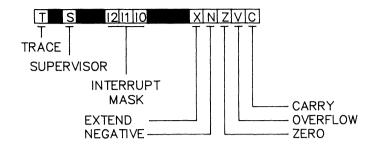

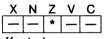

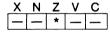

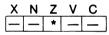

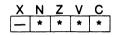

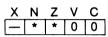

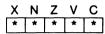

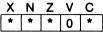

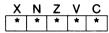

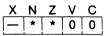

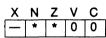

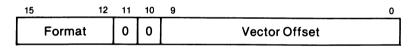

The 16-bit status register, shown in Fig. 2-8, is divided into two sections—the supervisor section and the user section. The latter is also called the *Condition Code Register*, simply to preserve some relation with the MC6800 register bearing the same name.

Fig. 2-8. Status register of MC68000.

The user portion of the status register is almost identical to that of the MC6800, with the added flag of Extend. This flag is asserted when a value is to be signextended for alignment purposes. The N flag is set when the result of an operation produces a negative value. The Z flag is set when the result of an operation produces a zero value (it is important to know when a division must use this value). The overflow flag, V, is set when an overflow results. The carry flag, C, is set when a carry occurs.

When the processor enters the Trace mode (as in a single-step operation, described later), the T flag is set. When the processor enters the supervisor mode because of a bus error or other condition, the S flag is set.

The three interrupt bits act as interrupt mask bits for the IPL lines. The interrupt flags are always set to a value lower than the one present on the IPL lines.

# Chapter 3 A Small MC68000 System

#### INTRODUCTION

This chapter explains the design of a small 68000-based system, beginning with the design of reset/halt circuits and the basic RAM and ROM system. Since the operation of most peripheral devices requires programming, peripheral devices will be examined after some exposure to the programming of the MC68000. This chapter will show how different signals are applied and provide various ways of interfacing them.

Since expansion of this system is contemplated, various features present in larger systems, such as buffering of the buses, will also be considered.

#### **BLOCK DIAGRAM AND MEMORY MAP**

The two main steps in the design of any microprocessor system are its definition both in words and block diagram form and the design of its memory map.

The MC68000 can be interfaced to other devices very easily. Any type of memory device can be used, from bytewide RAM to dynamic RAM. Since bytewide RAM is more expensive and physically larger than dynamic RAM, however, the latter will be used here. Some read-only memory is also needed to store the operating system program. Finally, serial circuits (for terminal and modem interface), parallel circuits (for printing), and audio cassette input-output circuits are needed.

#### **Block Diagram**

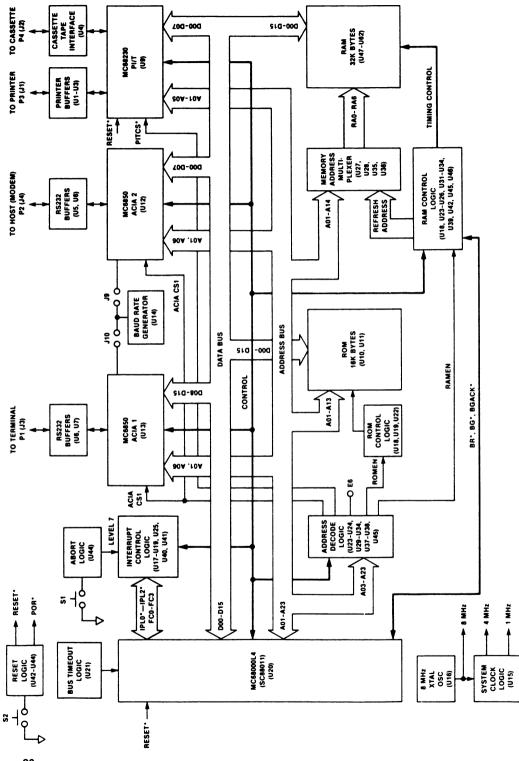

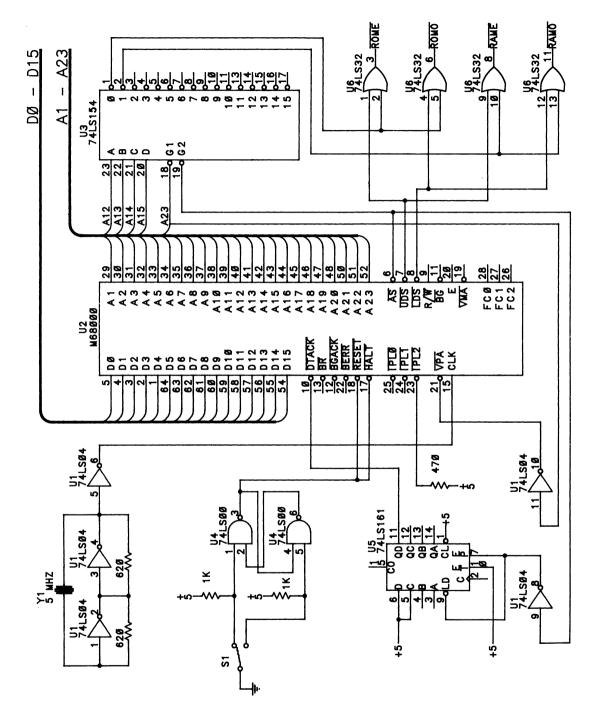

Figure 3-1 depicts a small, yet fully functional, system that fits our description. One of the slower versions of the MC68000-the MC68000L4 (4 MHz)-is used.

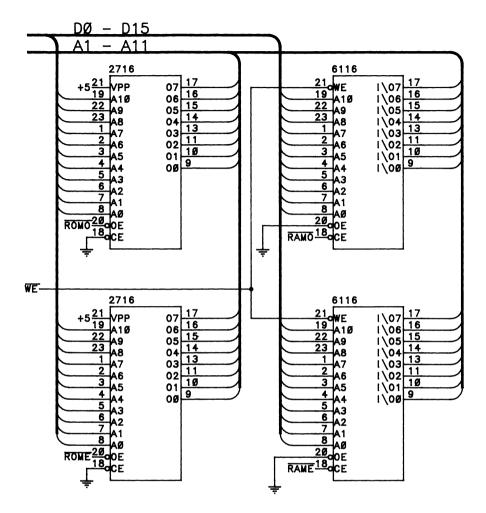

The RAM is the popular 4116,  $16K \times 1$  bit dynamic device. The system is equipped with 16 of these RAMs arranged as 16 kilowords ( $16K \times 16$ ). The ROM, which consists of two MC68A364,  $8K \times 8$  bit devices, is also arranged as 16 kilowords. The ROM is read on a byte or word basis. Provision must be made for the system not to waste time trying to write into ROM space if a user attempts to do so.

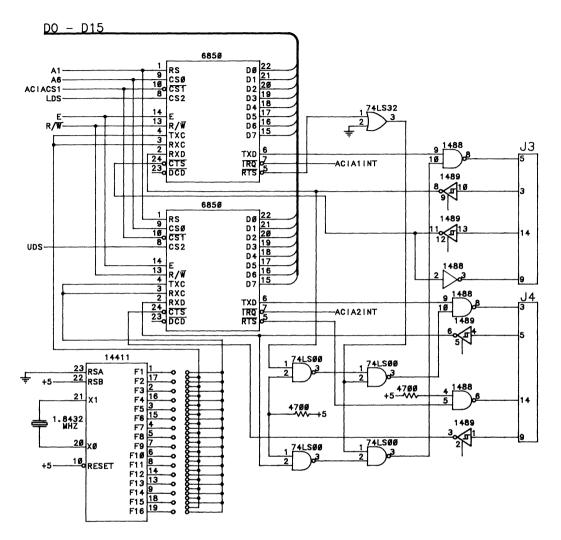

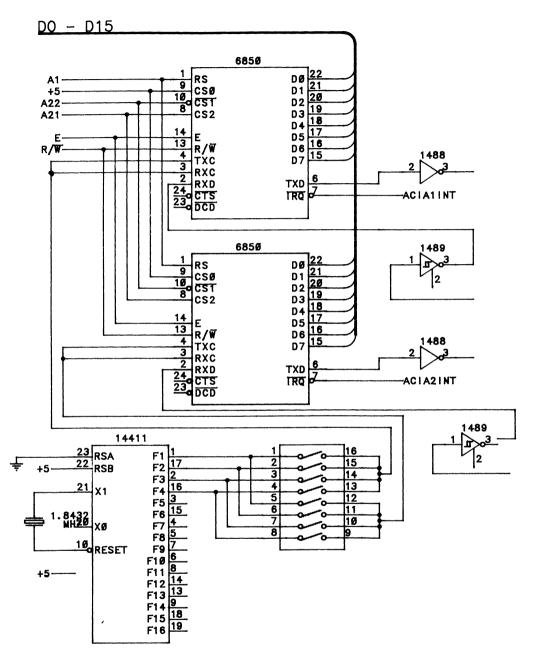

Two MC6850 (eight-bit) Asynchronous Communications Interface Adapters (ACIA) provide serial communication. One of these devices is used to interface with an external terminal and the other with a modern. A baud rate generator is included to provide variable clock rates for these devices.

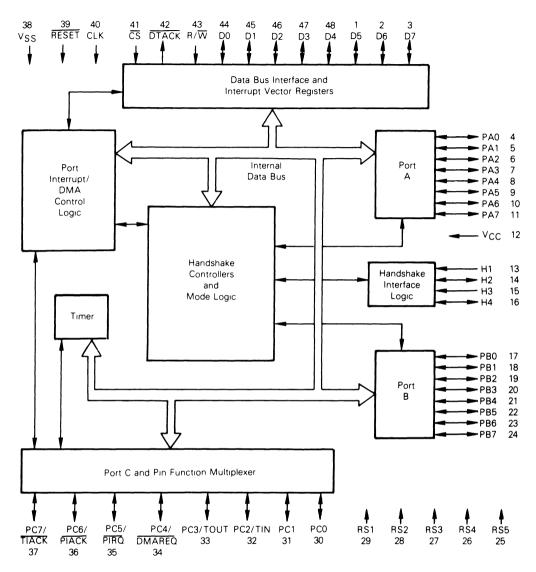

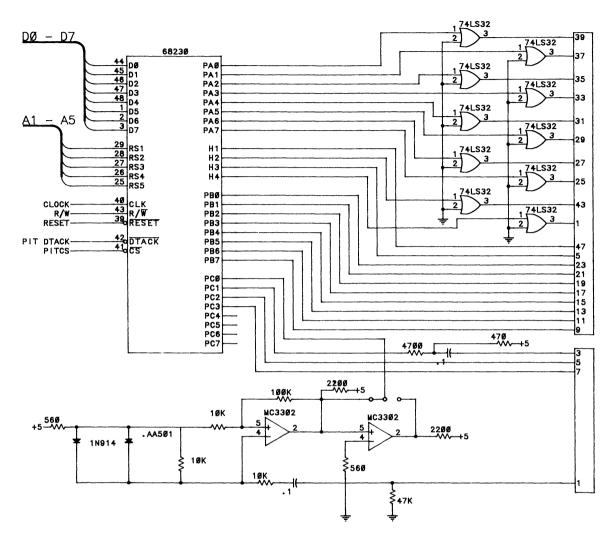

A MC68230 Parallel Interface/Timer (PI/T) furnishes the parallel interface and audio cassette functions.

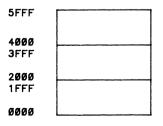

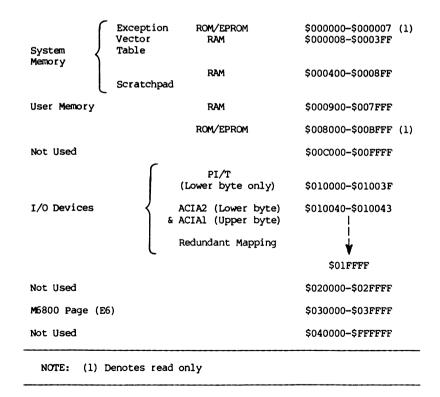

#### **Memory Map**

Figure 3-2 sets out the memory map of the system. Two requirements, set by Motorola, are that the table with the interrupt and trap vectors (256 in all) must be positioned at the bottom of the memory map of any MC68000 system (0000000 to 0003FF) and that the reset and stack pointer vectors must occupy the first eight locations. Since the system, whether on power-on or manual reset, must always load the same address into the program counter and system stack pointer without reloading the RAM each time, a small but clever trick is played—that is, overlapping the first eight locations of ROM and RAM. Thus, the contents that the program counter and system stack pointer

Fig. 3-2. Memory map of our system.

ROM permanently. Whether on power-on or manual reset, these eight locations can be loaded into RAM and thus become part of a vector table occupying 256 contiguous locations.

The remaining RAM area can be divided into two sections—one (from 000008 to 0008FF) to be used as a scratchpad for the operating system firmware; the other (from 000900 to 007FFF), to serve as the user memory area.

The ROM will reside in the area from 008000 to 00BFFF. The area from 00C000 to 00FFFF will be left open for future expansion or as a work area. The area from 010000 to 01FFFF will be occupied by the MC68230 and the two ACIA. Another unused area will be from 01FFFF to 02FFFF. The area from 030000 to 03FFFF will be left for the addition of any other MC6800 peripheral devices. One more unused area will be between 04000 and FFFFFF. All addresses are shown in hexadecimal notation.

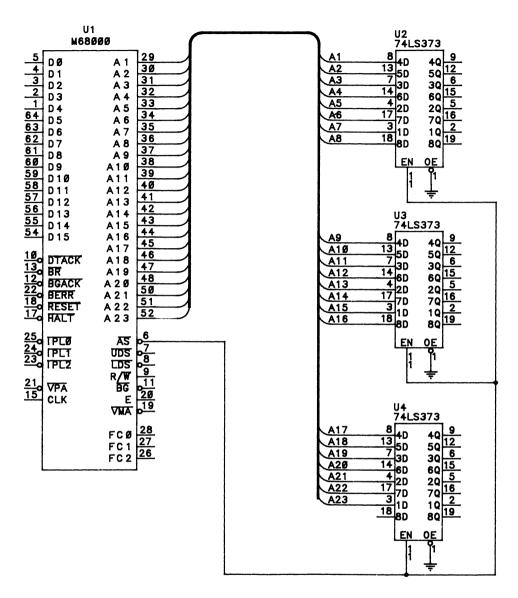

#### BUSES

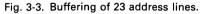

Although this system would function without address and data buffer devices, good design practice dictates that buffers be used whenever future expansion is contemplated. The schematic in Fig. 3-3 shows the buffering of the 23 address lines. Here, the 74LS373 latch is used as a buffer, but its latching input is disabled by its connection to the positive power supply via a pull-up resistor. Provision is made, however, for asserting the latching input by its connection to the  $\overline{AS}$  line via a jumper wire. An 8T97 buffer is used to buffer the  $\overline{AS}$  and other control lines. Some of the buffered lines are shown in Fig. 3-3.

Buffering of the data bus requires more thought. This bus is bidirectional, and the direction-enable signals of the buffers must be connected to the control signals of the MC68000.

The 74LS245 is an octal (eight-input, eight-output), noninverting, bidirectional buffer. In the schematic shown in Fig. 3-4, this device is asserted continuously by connecting the Chip Enable (Pin 19) to ground. The direction of the buffers can be controlled by the combination of gates shown.

When Pin 1 is asserted (active-low), direction is towards the MC68000. When Pin 1 is negated (high), direction is from the processor to the external devices. Thus, during a read operation, data are transferred to the MC68000 from either the low or high data byte. During a write operation, the R/W line negates the direction-enable pin of the buffer, allowing transfer of data to the data bus.

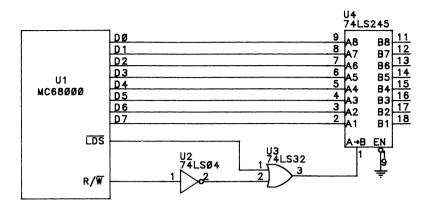

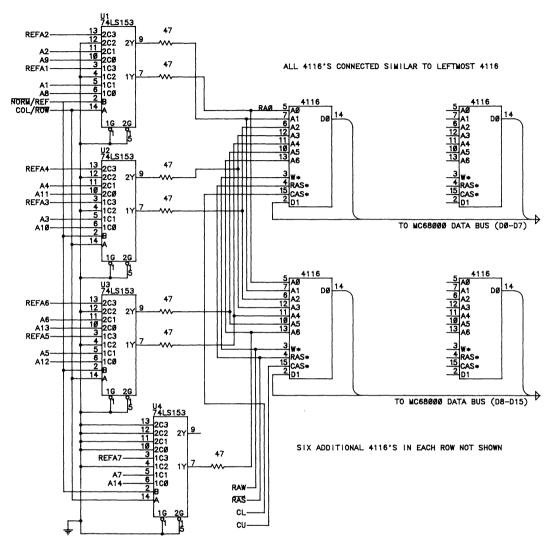

#### ADDRESS MULTIPLEXING

Since high-density dynamic RAMs are used, address lines A1 to A14 must be multiplexed in order to generate the row and column addresses required during read and write cycles. The multiplexers also provide refresh addresses to the RAM. The circuit in Fig. 3-5 shows the use of dual four-line to one-line 74LS153 multiplexers. The enable signals – Pins 1 and 15, respectively – are connected to ground so that the device may remain asserted at all times. Additional circuits associated with the decoding of the memory will be discussed in later sections.

Two circuits that can be designed at this stage are the reset/halt circuit and the system clock circuit.

#### **RESET/HALT AND SYSTEM CLOCK**

#### **Reset/Halt Circuit**

Several specifications must be taken into account before design of a reset/halt circuit is possible. The reset circuit must be able to serve the system both during

Fig. 3-4. Buffering using the 74LS245 octal noninverting bidirectional buffers.

the initial power-on and whenever a manual switch is pressed. The latter would function, for example, to release the system from a fatal error.

Motorola provides the following specifications for a reset/halt circuit: During power-on, the reset and halt signals should be asserted for slightly longer than 100 msec to allow for the stabilization of various internal circuits. When a manual switch is used, the reset and halt signals should be asserted for about ten clock cycles.

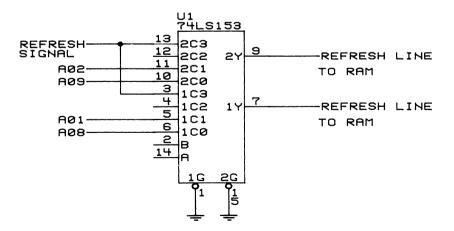

A reset-exception (a term to be discussed later) processing routine is executed after the reset signal is negated on the leading edge of a clock cycle. The flow chart in Fig. 3-6 shows the sequence of events that occurs during a reset.

During initiation of a reset, the (S)upervisor flag in the status register is set, the (T)race flag is reset, and the interrupt mask flags in the status register are set to seven. The next two steps set the system stack pointer; that is, vector

Fig. 3-5. MC68000 address multiplexing.

Fig. 3-6. Flowchart of the MC68000 reset activity.

number 00 is fetched from the vector table. At this point, the processor determines whether a bus error has occurred. If it hasn't, the contents of vector number 00 are transferred to the stack pointer. Vector number 01 is fetched next, and the bus-error possibility is re-examined. If two bus errors have occurred, the system enters a double bus fault condition, which normally is fatal and requires system reset. If not, the contents of vector number 01 are transferred to the program counter.

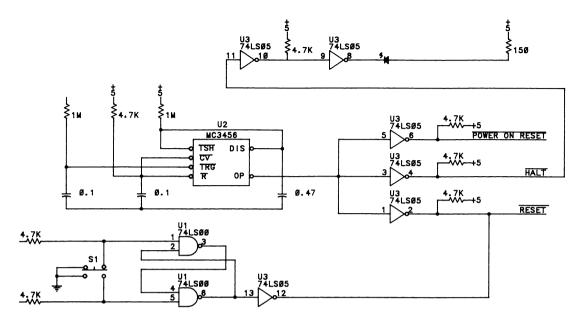

A combined reset/halt circuit is shown in Fig. 3-7. The circuit uses the MC3456 timer device, whose time-constant requirements are set by the resistor–capacitor combinations shown to satisfy the reset/halt, power-on timing specifications.

#### 26 THE 68000 MICROPROCESSOR

Fig. 3-7. An MC68000 combined reset/halt circuit.

The manual reset switch is debounced by a NAND flip-flop and is combined, through an OR gate, with the power-on reset signal from the timer and connected to the reset pin of the MC68000. The open-collector inverter satisfies the active–low input requirements of the MC68000 pin. The 2.2-k $\Omega$  pull-up resistor negates the reset input when the latter is not used.

The same OR-inverter arrangement is used on the halt input. A light-emitting diode is turned on when the halt signal is asserted. The halt signal may also be used as a single-instruction execution mechanism. In this case, a manual switch arrangement, similar to the reset, is connected to the signal through the OR and inverter gates.

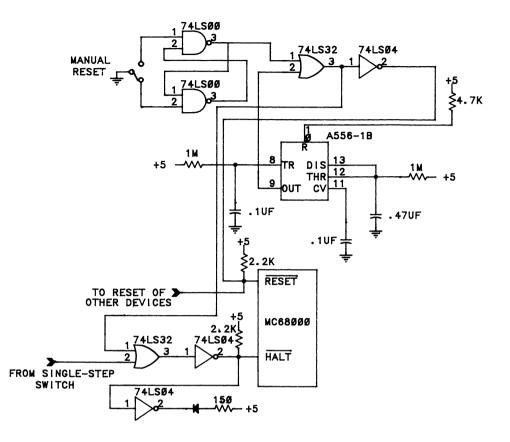

The circuit shown in Fig. 3-8–a slight modification of the previous one–is the circuit to be used in our small system. It produces a POR (Power On Reset) signal used in the ROM DTACK generation circuit (to be described later).

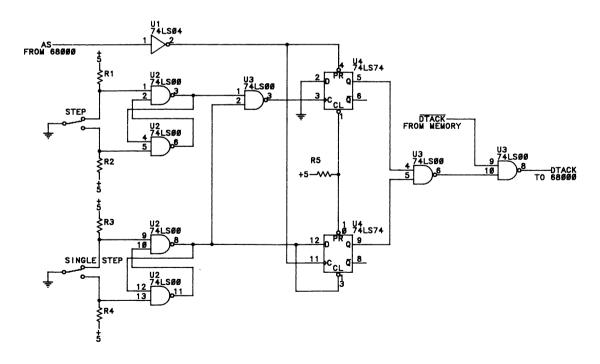

Although the small system does not include a single-step circuit, the design in Fig. 3-9 may be used for this purpose. Each time the  $\overline{AS}$  line is asserted, the flip-flop is reset. If the upper switch is in the single-step position, the processor

Fig. 3-8. Modified reset circuit used in our system.

Fig. 3-9. A single-step circuit.

#### 28 THE 68000 MICROPROCESSOR

halts and remains halted until the lower switch is toggled. In this way, the asynchronous buses can be controlled manually.

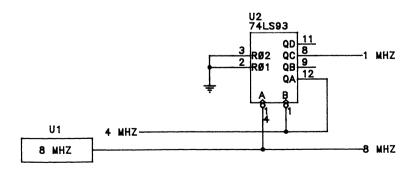

### System Clock

The small system uses a readily available, 8-MHz crystal oscillator, as shown in Fig. 3-10. A four-bit, ripple binary counter reduces this frequency to produce the 4-MHz clock frequency that the MC68000 needs and the 1-MHz frequency required by some peripheral devices. The system uses all three of the clock frequencies.

### TIMING

The speed with which a microprocessor executes instructions is of major concern to a design engineer. The small system includes components that permit appropriate future expansion, but the effect of these devices on the overall speed of the system have not been discussed.

In Chap. 2, the MC68000 was shown as being an asynchronous device, and the behavior of the DTACK lines supports this description. Synchronous operation of the MC68000 should not be excluded, however, since even its asynchronous lines are timed on a synchronous system clock.

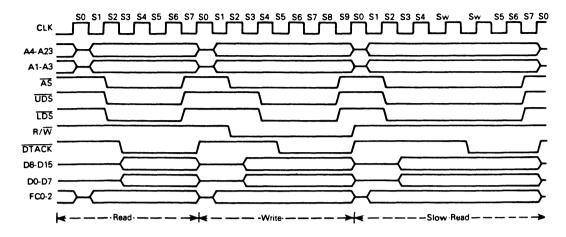

Figure 3-11 shows that all data and control lines are sensed on the leading edge and latched on the trailing edge of the system clock (shown in states, each full clock cycle being two S states). For example, the DTACK line is sensed, and asserted, one set-up time period before the trailing edge of state S4. If assertion occurs earlier than the set-up time of the trailing edge, a wait state of one full clock cycle is added to the timing. When DTACK becomes asserted on the trailing edge of the clock state, data are latched during the trailing edge of the next full clock cycle.

Thus, unless the DTACK signal is low for one set-up time, as required, the processor introduces wait states. Addition of these wait states, coupled with the presence of other devices, such as buffers or the gates used to generate the row address signal ( $\overline{RAS}$ ) in dynamic memories, may slow down a system.

Fig. 3-10. The oscillator circuit used in our system.

Fig. 3-11. Timing activity of the MC68000.

Table 3-1 indicates the operation, at nominal clock frequency, of an MC68000based system using RAM of various access times and Low-power Schottky (LS) or Schottky (S) devices. For example, consider using RAM with an access time of 150 nsec and LS buffers with a propagation delay of 56 nsec. The MC68000 at 8 MHz provides a total internal delay of 70 nsec; the AS to RAS delay is 22 nsec. Thus, the total bus latency is 298 nsec (sum of the above delays), and the system can operate (with no wait states) at a nominal frequency of 8 MHz.

The significant point, which Table 3-1 stresses, is cost of a system versus performance. For example, consider the last column of the table, showing the use of 450-nsec RAM and LS buffers. The critical path of  $\overline{AS}$  to  $\overline{RAS}$  is constant throughout the table. Thus, if slower and consequently cheaper RAM is used, it is seen that the lower clock speed (4-MHz) MC68000 must be used to avoid wait states. If a faster clock speed is chosen, then wait states must be introduced for the speeds of the processor and the RAM to be matched.

The factor of speed must be re-evaluated from the standpoint of instruction cycle time. The MC68000 requires a nominal read time of four clock periods – of which 2.5 are allocated to bus latency – and a nominal write cycle of five clock periods – of which 3.5 are allocated to bus latency. Thus, referring once more to Table 3-1, to avoid wait states but still afford the 348 nseconds of bus latency, a designer who uses 200-nsec RAMs and LS buffers must use either a 7.18-MHz clock or faster (Schottky) buffers.

Table 3-2 shows the operation of an MC68000 with 200-nsec RAMs and LS buffers. As shown, an ideal instruction of one read and one write consumes 17 clock cycles; with a system clock of 8 MHz (125 nsec), this represents 2125 nsec. In this case, a system provides 100-percent performance. The table also shows that, in nonideal (actual) operation, the system loses 15 percent of its performance, a percentage 3 percent higher than if a designer had decided to operate the system at a reduced clock frequency. The reason is simple: the MC68000 uses full cycles

| RAM ACCESS SPEC (NANOSECONDS)         50         100         150         150         150         250         250         250         250         300           Buffers 'S240 (4 × 7 ns)<br>'LS240, 8T26         28         28         28         28         28         28         28         56         56         56         56         56         56         56           AS - RAS         7         7         7         7         7         7         27         27         27         27         22         22         22         23         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         72         70         70         70         70         70         70         70         70         70         70         70         70         70         70         70         70         70         70         70         70         70         70         404         404         404 |                                                                                                                                               | -    |      |      |      | •    |      | )   |      |      | •    |     |      |      |      |     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-----|------|------|------|-----|------|------|------|-----|------|

| 28         28         28         28         28         28         28         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56         56<               | RAM ACCESS SPEC (NANOSECONDS)                                                                                                                 | 50   | 100  | 150  | 50   | 100  | 150  | 150 | 200  | 200  | 250  | 200 | 250  | 300  | 350  | 400 | 450  |

| 7 $7$ $7$ $7$ $7$ $7$ $22$ $7$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$ $22$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Buffers 'S240 (4 × 7 ns)<br>'LS240, 8T26                                                                                                      | 28   | 28   | 28   | 28   | 28   | 28   | 56  | 28   | 56   | 28   | 56  | 56   | 56   | 56   | 56  | 56   |

| V)         60         60         60         60         60         60         70         70         70         70         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90<               | AS – RAS                                                                                                                                      | 7    | 7    | 7    | 7    | 7    | 7    | 22  | 7    | 22   | 7    | 22  | 22   | 22   | 22   | 22  | 22   |

| (10 waits)*         145         195         245         145         195         245         248         305         348         355         368         418           (no waits)*         17.2         12.8         10.2         17.2         12.8         10.2         17.2         12.8         10.2         10.2         8.3         8.19         7.18         7.04         6.7         5.98           cv (no waits)*         12.5         10.2         10.0         10.0         8.0         8.0         7.18         7.04         6.7         5.98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MC68000 Delay<br>(Data Setup and AS Delay)<br>12.5 MHz (10 + 50)<br>10 MHz (10 + 50)<br>8 MHz (15 + 55)<br>6 MHz (25 + 65)<br>4 MHz (30 + 75) | 90   | 60   | 60   | 60   | 60   | 60   | 70  | 70   | 70   | 70   | 06  | 06   | 06   | 105  | 105 | 105  |

| (no waits)         17.2         12.8         10.2         17.2         12.8         10.2         12.8         10.2         8.3         8.19         7.18         7.04         6.7         5.98           cv (no waits)*         12.5         12.5         10.0         10.0         10.0         8.0         8.0         7.18         7.04         6.7         5.98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bus Latency                                                                                                                                   | 145  | 195  | 245  | 145  | 195  | 245  | 298 | 305  | 348  | 355  | 368 | 418  | 468  | 533  | 583 | 633  |

| cy (no waits)* 12.5 12.5 10.2 10.0 10.0 10.0 8.0 8.0 7.18 7.04 6.7 5.98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Max. Operating Frequency (no waits)                                                                                                           | 17.2 | 12.8 | 10.2 | 17.2 | 12.8 | 10.2 | 8.3 | 8.19 | 7.18 | 7.04 |     | 5.98 | 5.34 | 4.69 | 4.2 | 3.94 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Nominal Operating Frequency (no waits)*                                                                                                       |      |      | 10.2 | 10.0 | 10.0 | 10.0 | 8.0 |      |      | 7.04 | 6.7 | 5.98 | 5.34 | 4.0  | 4.0 | 3.94 |

Table 3-1. Operating Frequency for Various Operating Times (Courtesy, Motorola, Inc.).

\*Allowable within maximum clock frequency specified for MPU

| Table 3-2. Operation with LS Buffers and 200-nsec RAMs ( <i>Courtesy,</i> Motorola, Inc.).                                                    | n wit | h LS | Buffe | irs an | id 20( | 0-nse | c RAI | Ms (C | court | sy, I | Moto | rola, I | lnc.). |      |     |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|--------|--------|-------|-------|-------|-------|-------|------|---------|--------|------|-----|------|

| RAM ACCESS SPEC (NANOSECONDS)                                                                                                                 | 50    | 100  | 150   | 50     | 100    | 150   | 150   | 200   | 200   | 250   | 200  | 250     | 300    | 350  | 400 | 450  |

| Buffers 'S240 (4 × 7 ns)<br>'LS240, 8T26                                                                                                      | 28    | 28   | 28    | 28     | 28     | 28    | 56    | 28    | 56    | 28    | 56   | 56      | 56     | 56   | 56  | 56   |

| AS – RAS                                                                                                                                      | 7     | 7    | 7     | 7      | 7      | 7     | 22    | 7     | 22    | 7     | 22   | 22      | 22     | 22   | 22  | 22   |

| MC68000 Delay<br>(Data Setup and AS Delay)<br>12.5 MHz (10 + 50)<br>10 MHz (10 + 50)<br>8 MHz (15 + 55)<br>6 MHz (25 + 65)<br>4 MHz (30 + 75) | 60    | 60   | 60    | 60     | 60     | 60    | 70    | 70    | 70    | 70    | 06   | 06      | 06     | 105  | 105 | 105  |

| Bus Latency                                                                                                                                   | 145   | 195  | 245   | 145    | 195    | 245   | 298   | 305   | 348   | 355   | 368  | 418     | 468    | 533  | 583 | 633  |

| Max. Operating Frequency (no waits)                                                                                                           | 17.2  | 12.8 | 10.2  | 17.2   | 12.8   | 10.2  | 8.3   | 8.19  | 7.18  | 7.04  | 6.7  | 5.98    | 5.34   | 4.69 | 4.2 | 3.94 |

| Nominal Operating Frequency (no waits)*                                                                                                       | 12.5  | 12.5 | 10.2  | 10.0   | 10.0   | 10.0  | 8.0   | 8.0   | 7.18  | 7.04  | 6.7  | 5.98    | 5.34   | 4.0  | 4.0 | 3.94 |

|                                                                                                                                               |       |      |       |        |        |       |       |       |       |       |      |         |        |      |     |      |

| Ĕ          |

|------------|

| Motorola,  |

| ~          |

| (Courtes   |

| ്          |

| RAMs       |

| Š          |

| -nse       |

| 2          |

| 200        |

| and        |

| Buffers    |

| Buffe      |

| LS B       |

| 2          |

| witl       |

| E C        |

| Ë          |

| erat       |

| ő          |

| Ξ.         |

| Ņ          |

| Ó          |

| Table 3-2. |

|            |

\*Allowable within maximum clock frequency specified for MPU

as wait states. Thus, a cost savings can be effected here by using 250-nsec RAMs with Schottky buffers. The overall performance remains the same.

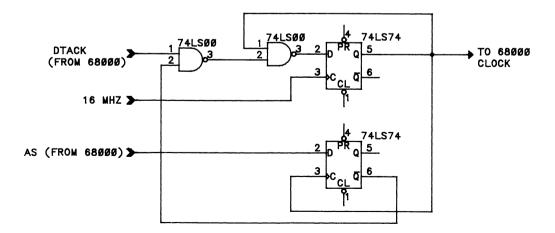

As the last line in Table 3-2 indicates, performance may be improved further if the full cycle of wait states can be reduced by, say, 50 percent. Doing so is not impossible if flip-flops are used, as shown in Fig. 3-12. The clock-stretching circuit shown here will extend S4 (the DTACK latching cycle) by unit periods of the oscillator input to the flip-flop. This circuit, however, will not stretch S2 since data strobes are not output until S3 of a write cycle.

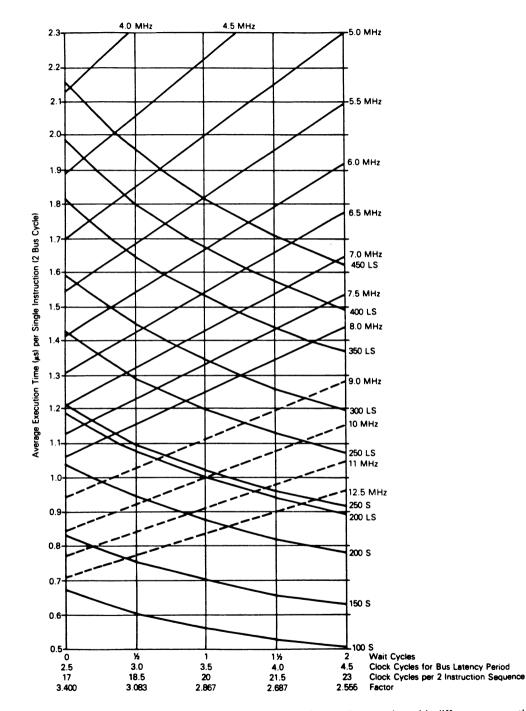

A useful chart by which the performance of a system can be evaluated appears in Fig. 3-13. The left-hand side of the chart denotes, in microseconds, the average execution time of a single two-bus-cycle instruction. The nominal clock frequencies are the lines sloping downward from right to left. Memory access times are the lines sloping upward from right to left. In the case of 200-nsec and 250-nsec RAM, two curves are given – one for RAM buffered with Schottky devices and the other for RAM buffered with Low-power Schottky devices. Values such as wait states and cycle time are given at the bottom of the chart; these are used in conjunction with the other sections.

Let us use some values in Table 3-2 derived from this chart. The 8-MHz clock line crosses the 0-wait-state line between the area of the 200 LS RAM and the 200 S RAM. Using Schottky buffers and excluding wait states, the bottom of the chart shows that a two-instruction sequence can be executed in 17 cycles, or 2.12  $\mu$ sec (i.e., two times the 1.06- $\mu$ sec point on the chart).

The use of LS buffers and 200-nsec RAM would require one wait state, and the execution time would increase to 2.5  $\mu$ sec. With a circuit similar to that in Fig. 3-12, however, the execution time will drop to 2.32  $\mu$ sec.

The chart also allows comparison of performance in speed at various clock frequencies, RAM access time, and LS or S buffers. For example, the execution time does not vary significantly at 6-MHz/250-nsec RAM (1.42  $\mu$ sec), 6.41-MHz/300-

Fig. 3-12. Clock stretching circuit using flip-flops.

Fig. 3-13. Performance of a MC68000 using various TTL devices and memories with different access times.

nsec RAM (1.44  $\mu$ sec) or 7-MHz/300-nsec RAM (1.43  $\mu$ sec).

The bottom line of the chart provides values ("factors") that can be used to plot a memory system—that is, when a factor is multiplied by the total required bus latency, the product is the average execution time per simple instruction for the indicated occurrence of wait states for the particular two-instruction sequence.

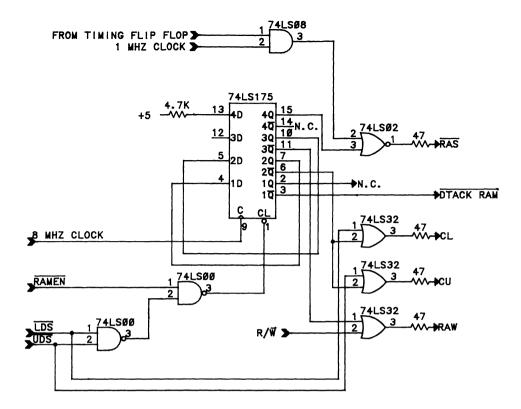

# **BUS TIMEOUT LOGIC**

It was mentioned earlier that some provision must be made to avoid wasting time if, for instance, writing into ROM memory space should be attempted. Addressing of an unused location in a memory area or failure of a circuit to respond will also waste time.

The circuit in Fig. 3-14-usually called a "watchdog timer"-consists of a 74LS175, quad D-type flip-flop, which is connected as a four-bit serial shift register. After the circuit is cleared via the  $\overline{AS}$  line, four clock cycles taken from the E clock of the MC68000\* are "walked" through it. A total delay, or bus timeout, of 10  $\mu$ sec is produced.

# **DESIGN OF RAM AND ROM INTERFACE**

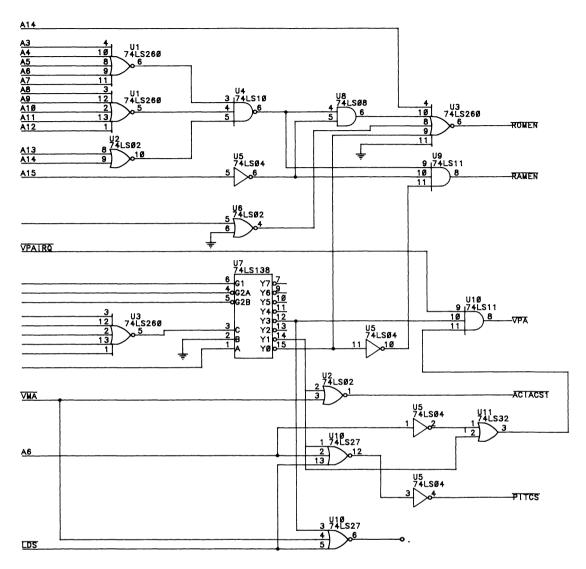

Several circuit groups must be used for the interface of the RAM and ROM. The first circuit must be a general decoding circuit for the RAM, ROM, and some MC6800 peripheral devices (the latter are also part of a memory-mapped scheme). Since use of these peripheral devices is planned, a VPA bus termination signal must also be generated. The circuit in Fig. 3-15 demonstrates a general decoding scheme for the small system under study here.

Gates U1, U2, U3, U4, U5, U6, U7, U8, U9, U10, and U11 decode address lines A3 to A15. These gates are combined with the output of the 74LS138 decoder (U30) to generate a ROM enable signal (ROMEN) in the address area from 008000 to 00BFFF and a RAM enable signal (RAMEN) in the area from 000008 to 007FFF. The address range selected is shown at the output of the corresponding gate in Fig. 3-15.

Gate U4 performs an interesting task. As mentioned earlier, the first eight memory locations are overlapped by RAM and ROM. The output of this gate is used to assert the ROMEN and RAMEN signals in this memory area.

The 74LS138 decoder also selects the memory areas for ACIA (010040 to 010043) and the parallel interface/timer device (01000 to 0103F). Several outputs of this decoder are not connected and can be used for future expansion within the unused memory-map areas.

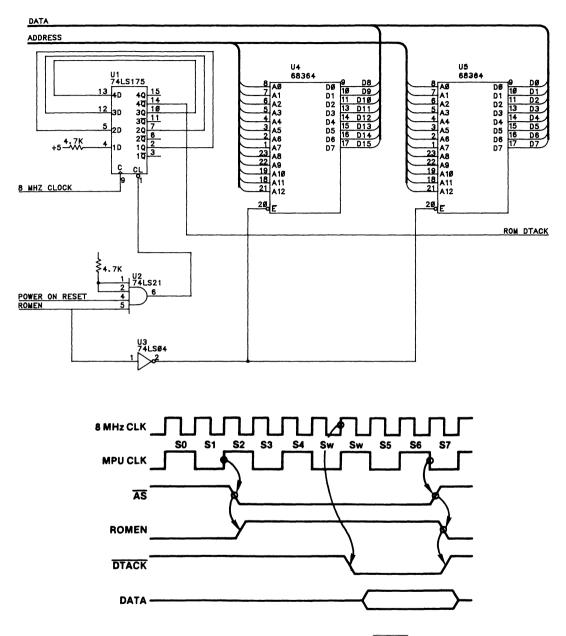

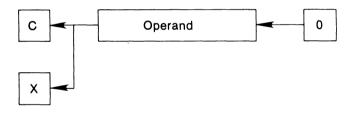

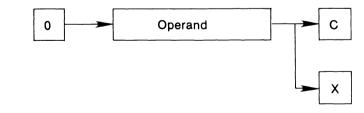

# **ROM Circuit**

Two MC68A364 ROM are used, as shown in Fig. 3-16. Each has a storage capacity of 8 kilobytes times 8 bits (8 kilowords). When the ROMEN enable signal

<sup>\*</sup>E = MPU clock/10; in this case, E = 400 kHz. Each stage provides a delay of 2.5  $\mu$ sec (total of 10  $\mu$ sec).

Fig. 3-14. Watchdog timer.

selects both devices simultaneously, the total ROM space is 16 kilobytes (or 8 kilowords) times 16 bits (16 kilowords).

The MC68A364 has various access-time speeds. For economy, we will select the slow (350-nsec) version.

The function of the DTACK generation circuit with respect to the ROM is illustrated by the timing diagram in Fig. 3-16. The AS and ROMEN signals are asserted on the leading edge of S2, and DTACK is sensed on the leading edge of S4. Since a slow memory has been chosen, however, the timer must assert DTACK later than S4 (in about 500 to 625 nsec). When the system senses that DTACK is not present, it introduces wait states. When DTACK is finally asserted, data are sensed (S5) and latched (S6).

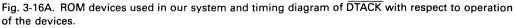

## **RAM Circuit**

The choice of a slow dynamic RAM (450-nsec) for our system means that a timer circuit must be designed for the DTACK. A circuit must also refresh the DRAM,

Fig. 3-15. RAM-ROM decoding circuit for our system.

usually once every 1.5 msec, and preferably while the processor is not busy with the buses. The direct-memory access signals are prime candidates for this circuit. Furthermore, a technique called *RAS refresh only* can be used. This dynamic, memory-refresh technique is appropriate with asynchronous systems since it is not possible to accomplish a memory refresh in such systems without interfering with the processor cycles. When a high-priority RAS refresh request is generated, a refresh cycle is initiated at the completion of a processor cycle in progress.

This technique is called *cycle stealing*. The memory-cycle requests from the processor are interrupted and a refresh cycle inserted in their place; thus, a normal cycle is stolen from the processor to carry out refreshing of the memory.

In large systems, arbitration circuits are used to accommodate the cyclestealing technique. In our small system, however, a simple handshake approach of a request ( $\overline{BR}$ ), grant ( $\overline{BG}$ ), and acknowledge ( $\overline{BGACK}$ ) is sufficient.

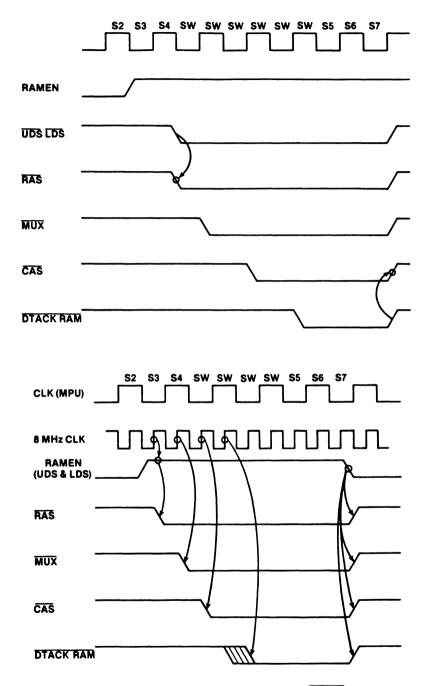

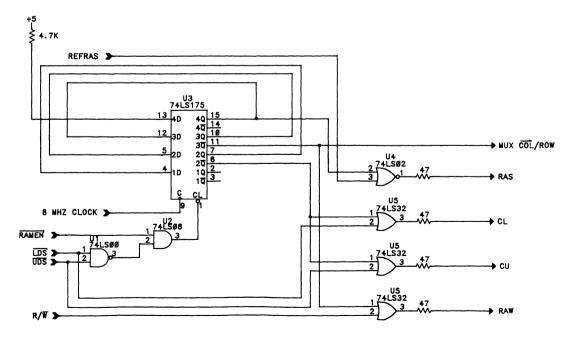

The timer circuit for our system is shown in Fig. 3-17. This circuit provides the following control signals:

#### 38 THE 68000 MICROPROCESSOR

Fig. 3-16B. ROM devices used in our system and timing diagram of  $\overline{\text{DTACK}}$  with respect to operation of the devices.

Fig. 3-17. Timer circuit.

Fig. 3-18. Cycle stealing method.

Fig. 3-19. Timing and addressing circuit for our system.

- 1. Column/Row multiplex signal used to select the 74LS153 multiplexers

- 2. DTACK RAM used to signal DTACK to the MC68000

- 3.  $\overline{RAS}$  used to refresh the row addresses of the DRAM

- CU, CL (Upper Column, Lower Column) used to select either the upper or lower columns of the DRAM

- 5. RAW-used as a read/write signal

A second circuit, depicted in Fig. 3-18, carries out the cycle-stealing technique. This circuit is, essentially, a timing circuit, controlled by the handshake signals mentioned earlier. It generates the signals to assert the 74LS153 multiplexers. Combined with the circuit in Fig. 3-17, it forms the timing and addressing circuit for the DRAM. The complete memory circuit is shown in Fig. 3-19.

Completion of the memory circuit temporarily suspends discussion of the MC68000 hardware features. This discussion will be resumed when the programming features necessary for the design of input-output and interrupt circuits have been described.

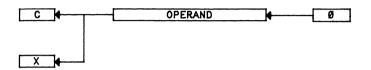

# Chapter 4 Addressing Modes; Instruction Set

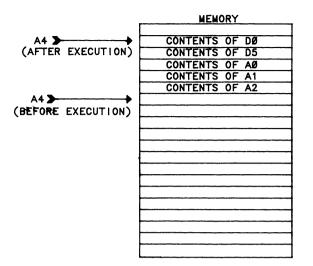

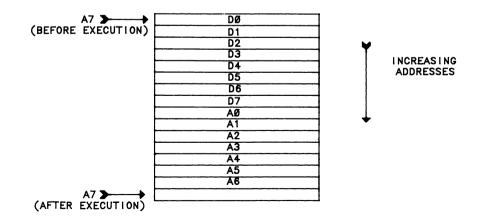

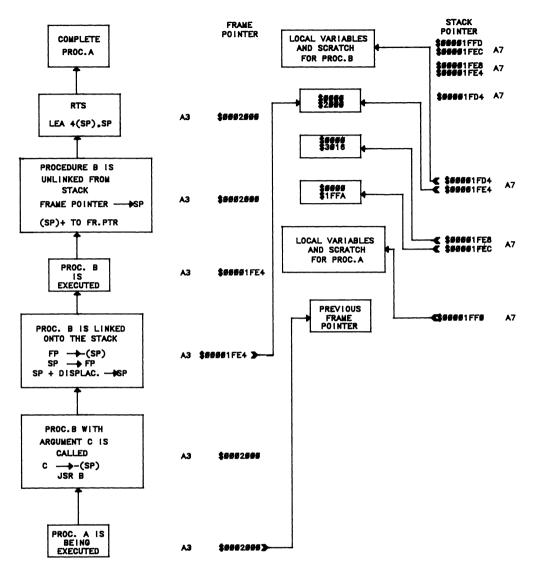

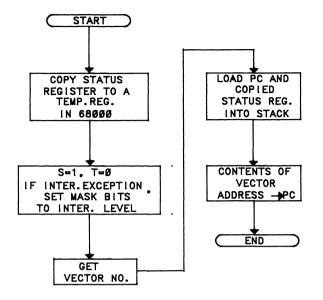

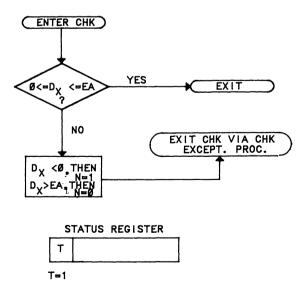

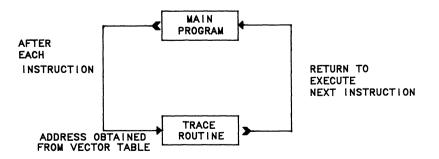

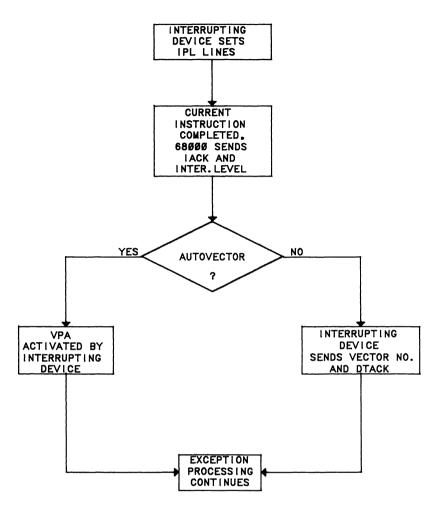

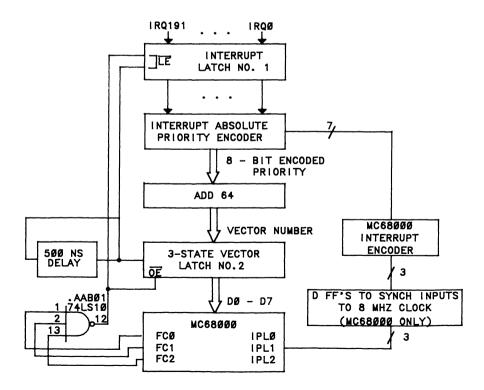

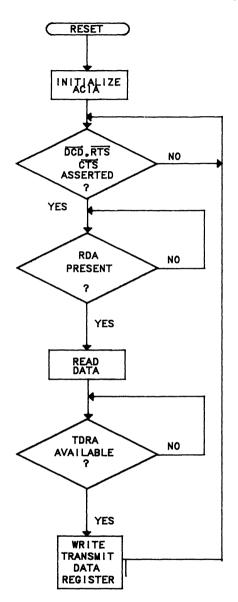

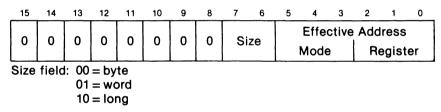

## ADDRESSING MODES