**Robert Erskine**

RST

ASSEMBL9 ASSEMBL9 ASSEMBL9

### First Steps in Assembly Language for the 68000

Robert Erskine

#### **Glentop Press Ltd**

#### Dedicated to Tom and Margaret

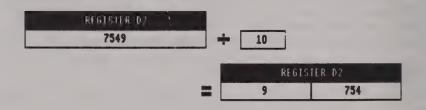

#### **MAY 1987**

All programs in this book have been written expressly to illustrate specific teaching points. They are not warranted as being suitable for any particular application. Every care has been taken in the writing and presentation of this book but no responsibility is assumed by the author or publishers for any errors or omissions contained herein.

COPYRIGHT

© Glentop Press Ltd 1987 World rights reserved

No part of this publication may be copied, transmitted or stored in a retrieval system or reproduced in any way including but not limited to photography, photocopy, magnetic or other recording means, without prior permission from the publishers, with the exception of material entered and executed on a computer system for the reader's own use

#### ISBN 1 85181 081 1

Published by:

Glentop Press Ltd Standfast House Bath Place High Street Barnet Herts EN5 5XE Tel: (01) 441 4130

Originated directly from the publisher's w-p disks by NWL Editorial Services, Tel (0458) 250834

Motorola 68000 assembly language mnemonics are the copyright of Motorola Inc.

Printed in Great Britain by Ashford Colour Press Gosport, Hampshire

# Contents

| PART I        |                                                |         |

|---------------|------------------------------------------------|---------|

| Introduction  |                                                | xi      |

| Chapter 1     | Beginning Assembly Language                    | 1       |

|               | Memory, Addresses and Data<br>Bytes            | 2       |

|               | Words and Long Words                           | 5       |

|               | The Memory Map                                 | 7<br>10 |

|               | Program and Data Storage                       | 10      |

|               | Assemblers                                     | 12      |

| Chapter 2     | <b>Registers and Addressing Modes</b>          | 21      |

| 12 21         | Sources and destinations                       | 21      |

|               | Registers                                      | 21      |

|               | Data Registers                                 | 22      |

|               | Address Registers                              | 23      |

|               | Additional Registers                           | 23      |

|               | Addressing Modes                               | 24      |

|               | Implicit Addressing                            | 25      |

|               | Register Direct Addressing                     | 25      |

|               | Absolute Addressing                            | 29      |

|               | Immediate Addressing                           | 30      |

|               | Address Register Indirect Addressing           | 31      |

|               | Address Register Indirect                      | 24      |

|               | with Postincrement                             | 34      |

| Constant D.C. | Address Register Indirect<br>with Predecrement | 24      |

|               | Address Register Indirect                      | 34      |

|               | with Displacement                              | 34      |

|               | Address Register Indirect                      | 54      |

|               | with Index and Displacement                    | 35      |

|               | Program Counter Relative Addressing            | 37      |

| Chapter 3     | Condition Flags                                | 39      |

|               | Zero Flag (Z)                                  | 41      |

|               | Sign Flag (N)                                  | 41 43   |

|               | Carry Flag (C)                                 | 45      |

|               | Overflow Flag (V)                              | 48      |

|               |                                                | 10      |

|           | Extend Flag (X)                           | 49  |

|-----------|-------------------------------------------|-----|

|           | Conditional Suffixes                      | 49  |

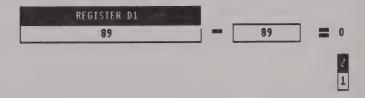

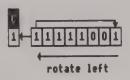

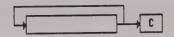

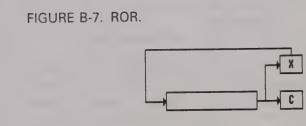

|           | Bit Rotation                              | 51  |

|           | Logical Operations                        | 53  |

|           | Specific Flag-altering Instructions       | 54  |

|           | Flag Testing                              | 54  |

| Chapter 4 | Branching Operations                      | 57  |

|           | Relative Addressing                       | 57  |

|           | Jump Operations                           | 58  |

|           | Branch Operations                         | 59  |

|           | Labelled Branching Operations             | 60  |

|           | Absolute and Indirect Branching           | 62  |

|           | Conditional Branching                     | 63  |

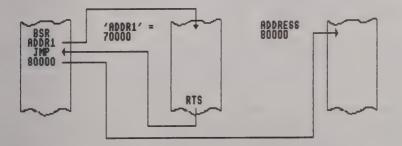

|           | Subroutines                               | 66  |

|           | Passing Parameters to Subroutines         | 67  |

| Chapter 5 | The Stack                                 | 71  |

|           | Reverse Stacks                            | 76  |

|           | Queues                                    | 76  |

|           | Altering Return Addresses                 | 77  |

|           | Passing Parameters via the Stack          | 79  |

|           | Stack Frames                              | 80  |

| Chapter 6 | Data Structures                           | 83  |

|           | Indexing Look-up Tables                   | 88  |

|           | Block Instructions                        | 89  |

|           | Altering Indexed Blocks                   | 91  |

|           | Sorting Data                              | 95  |

|           | Program Positioning and Labelling         | 96  |

| Chapter 7 | Exceptions, I/O and Arithmetic Operations | 99  |

|           | Exceptions                                | 99  |

|           | Operation of Exceptions                   | 100 |

|           | Exception Priority System                 | 101 |

|           | Internal Exceptions                       | 102 |

|           | External Exceptions                       | 103 |

|           | Exception Vector Table                    | 104 |

|           | Input and Output Operations               | 105 |

|           | Binary Arithmetic                         | 105 |

|           | Binary-coded Decimal Arithmetic           | 108 |

#### PART II

| Chapter 8  | Assembling Programs                     | 115 |

|------------|-----------------------------------------|-----|

|            | Data Sizes                              | 115 |

|            | Hexadecimal Numbering                   | 116 |

|            | Assembler Programs                      | 118 |

|            | Assembler Structure                     | 118 |

|            | Example Program 1                       | 120 |

|            | Linking Program Segments                | 126 |

|            | Tracing a Program                       | 129 |

|            | Data Dumps                              | 130 |

|            | Executing a Machine-code Program        | 131 |

| Chapter 9  | Addressing Modes                        | 135 |

|            | Register Model                          | 135 |

|            | Register Descriptions                   | 136 |

|            | Addressing Modes                        | 139 |

|            | Addressing Mode Classifications         | 146 |

|            | Example Program 2                       | 148 |

| Chapter 10 | Status and Condition Flags              | 161 |

|            | The Status Register                     | 161 |

|            | Zero Flag                               | 162 |

|            | Sign Flag                               | 163 |

|            | Overflow Flag                           | 164 |

|            | Carry Flag                              | 164 |

|            | Extend Flag                             | 165 |

|            | Status Flags                            | 166 |

|            | Flag Control Instructions               | 167 |

| Chapter 11 | Conditional and Unconditional Branching | 169 |

|            | Short and Long Branching                | 169 |

|            | Conditional Branches                    | 170 |

|            | Unconditional Branches and Jumps        | 171 |

|            | Conditional Branching to Subroutines    | 172 |

|            | Returning from Subroutines              | 173 |

|            | Example Program 3                       | 174 |

|            | Passing Parameters to Subroutines       | 178 |

|            | Example Program 4                       | 179 |

|            | Subroutine Returns                      | 184 |

|            | Linking Programs                        | 185 |

| Chapter 12 | Stack Operations                                                                                                                                           | 189                                           |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|            | Example Program 5                                                                                                                                          | 190                                           |

| Chapter 13 | Data Structures and Data Processing                                                                                                                        | 197                                           |

|            | Sorting Data<br>Example Program 6                                                                                                                          | 219<br>219                                    |

| Chapter 14 | Debugging, Instruction Formats and<br>Supervisor Mode Operation                                                                                            | 221                                           |

|            | Program Debugging<br>Assembly Errors<br>Trial Run<br>Debugging Monitor<br>Instruction Opcpde Formats<br>Supervisor-mode Operation                          | 221<br>223<br>223<br>223<br>225<br>227<br>229 |

|            | Memory Management System                                                                                                                                   | 229                                           |

| Afterword  |                                                                                                                                                            | 231                                           |

| APPENDICE  | ES                                                                                                                                                         |                                               |

| Appendix A | Instructions by Category                                                                                                                                   | 237                                           |

| Appendix B | Instruction Glossary                                                                                                                                       | 241                                           |

|            | Key to Abbreviations<br>Instruction Glossary                                                                                                               | 241<br>242                                    |

| Appendix C | Conversion Table                                                                                                                                           | 269                                           |

|            | Converting from Hexadecimal to Decimal<br>Converting from Decimal to Hexadecimal<br>Converting from Decimal to Binary<br>Converting from Binary to Decimal | 269<br>270<br>270<br>271                      |

|            | Converting from Hex to Binary<br>and Binary to Hex                                                                                                         | 271                                           |

| INDEX      |                                                                                                                                                            | 273                                           |

|            |                                                                                                                                                            |                                               |

|            |                                                                                                                                                            |                                               |

### Introduction

You may already have had some experience of programming a computer in assembly language. If you have, the likelihood is that at some point you have lost the thread of understanding, either because the books you have read have been too technical or because the unfamiliar concepts of assembly language have not been clearly related to concepts which are already familiar to you.

It is one thing to learn a language like BASIC, in which instructions like PRINT and GOTO mean exactly what they appear to mean, and another thing altogether to deal with assembly language, in which numbers whose significance is often unclear are manipulated by strange and abstract instructions to produce further numbers whose purpose seems equally vague. Like a traveller without a map in a foreign land, you are stuck with a strange language and a strange currency and can find no means of orienting yourself.

It is important however, not to think of programming purely in terms of learning language instructions. Programming is mostly about using your imagination to see how a particular process or concept might work and how it might best be structured and manipulated in memory. The actual program instructions are merely a means to this end and you need not worry too much about trying to learn and memorize them all as most of them will tend to become familiar through experience. It is far more important to understand the key concepts of programming and the standard program structures which enable you to translate your ideas into easily manageable modules of code. For this reason, this book does not try to be a comprehensive text book covering every detail of each instruction code, although a large number of program instructions will be explained and illustrated in the text and a complete list of them, with descriptions of their functions, is given in Appendix B. At a later stage you may wish to purchase a more formal book containing comprehensive technical reference information, although for ordinary practical purposes you will find that this book contains most that the general applications programmer needs to know.

One thing that would come in very useful would be an assembly language reference manual relating specifically to your computer. Although 68000 assembly language works the same way for all 68000 based computers there are always significant differences between one machine and another; the major ones being the different operating systems which are used and secondly, the structure of the display screen.

The differences between operating systems are significant because they provide a means of accessing some of their subroutines directly from within your own assembly language programs. Different systems will provide different sets of routines and the methods of accessing them may vary between one computer and another. Additionally, some computer systems may have less 'transparent' operating systems than others. They may, for example, have a layer of user-interfaces such as BASIC or window and icon programs which can sometimes make the operating system difficult to get at directly.

The differences between screen structures are more obvious because the height and width of the display, the degree of graphic resolution, the number of colours used and the way in which colors and images are coded will vary considerably.

In the technical reference manual available for your computer you should find all the information you need for integrating these facilities and features in your programs. If this information is not supplied then it is worth checking your local bookstore for independently published books which relate to your particular machine or operating system.

Because of this wide variation in design, it is not possible in this volume to explain the operation of certain types of functions, such as line graphics, for different makes of computer. However, the insights into programming methods which you will acquire, together with the information contained in your own technical manuals, should enable you to construct graphics routines without much difficulty.

We are going to be taking things gradually, avoiding the technicalities of the computer's circuitry and concentrating on the most important aspect of programming: how to translate the ideas and concepts which are in your imagination into program structures which will enable them to be carried out.

In the first few chapters we shall be building up the broad outlines of

assembly language programming. Chapters 1 to 7 in Part I will mainly be general, illustrating topics common to most assembly language programming as well as facts and concepts relating to the 68000 chip in particular.

You will find it helpful to think of assembly language programming in terms of a group of key concepts which are common to all assembly language programs, such as data storage, data addressing and the use of registers, the use of flags, conditional branching, using stacks and referencing indexed tables of data. Chapters 1 to 6 are based on each of these concepts and in chapter 7 we shall look at some miscellaneous aspects of programming and system operation.

The corresponding chapters in Part II will deal in detail with the 68000, with much more emphasis on the use of its programming instruction set. Chapters 8 to 13 summarize the main concepts outlined in Part I and illustrate their applications using a number of complete and annotated programs. The multi-user, multi-tasking and protection capabilities of the 68000 will be outlined in Chapter 14, together with notes on program debugging and object code formats. An extensive appendix contains descriptions of the complete instruction set.

The programs in Part II are fairly simple, functional routines which are designed to help you learn to use instructions by example, in a meaningful context, rather than by the more common method of learning the functions of each group of instruction types in a more formal way.

They illustrate some of the more important programming functions such as setting up variables and arrays, printing characters and sentences to the display screen, arithmetical operations and processing stored data. They all follow a fairly similar structure so that they tend to reinforce understanding and most of the instructions used will appear frequently so that their functions will become familiar as you read through the chapters. If you experience any difficulty in understanding how a particular process works, don't worry too much. The more complex functions which you come across will be explained in the same chapter or later in the book and it is better to read on and come back to something than to become stuck over a point of detail.

Each chapter deals with a particular topic and on a first reading of Part II you will find it more useful to concentrate on the topics illustrated

by the example programs than to try to follow everything contained in them.

To begin with you may prefer to read through Parts I & II in sequence and then later, you can read the corresponding chapters in each part in conjunction in order to reinforce your understanding.

#### User and Supervisor Modes

The 68000 operates in two modes: user and supervisor mode. In practice you will normally only be concerned with user mode which is the mode in which ordinary user programs are executed. Supervisor mode is used by the computers's operating system in order to gain total supervisory control over the events taking place in the system. Supervisor mode is only mentioned in the text of this book in relation to special system functions and it is not necessary for you to have any detailed knowledge of its operation.

## Part I

## Chapter 1

### **Beginning Assembly Language**

Assembly language, or 'machine code', consists of coded instructions which instruct the machine – or more accurately the processor – what to do. Machine code is a purely numeric form of assembly code, but when programs are written it is usual to use a set of non-numeric instructions called *mnemonics*, which are directly equivalent to machine code and are a lot easier for mere humans to understand.

Assembly language is the term used to describe this set of mnemonic instructions and the two terms will be used in their appropriate contexts throughout the book to distinguish the two forms of code. Programming in pure numeric machine code is possible and is very often done on old, 8-bit computers. With a complex processor like the 68000 you would need to be very fond of numbers to want to write your programs in this way and the programs in this book are presented in their assembly language format.

Although many of the concepts involved are similar to those used in BASIC, many are quite different and it is best to approach the subject without too many pre-formed notions. Think of the computer initially as a machine consisting of nothing but a keyboard, a processor, a screen and so many memory locations, say 256 000.

Starting from this uncluttered viewpoint, the principles of assembly language programming become extremely simple.

Consider the following facts:

- 1 All programs, data, colour and graphics must consist of numeric data.

- 2 Everything which the computer does, such as arithmetic calculations and the printing of letters, numbers and graphics on the screen, is performed on data taken either from memory or from some peripheral device such as the keyboard or a disc drive.

3 The CPU (central processing unit, or microprocessor) performs all arithmetic operations and controls and co-ordinates the movement of data between itself, memory, the keyboard, the VDU (visual display unit) screen and other peripheral devices.

These three facts represent the basic model of a processing system.

Unlike a high level language such as BASIC, which is designed to coordinate sets of general concepts, grouped under function names such as PRINT, LIST, LOG, CLS and so on, the function of assembly language is simply to direct the CPU to control the sequence of individual data movements around the system. In the next few chapters we shall be exploring not only how this is done but also how the movement of data relates to recognizable functions such as arithmetic calculation and the printing of characters and words to the screen. It is important, before you begin to learn these techniques, to acquire a general understanding of how data is stored and manipulated, because it is much easier to develop a program in assembly language if you are able to construct in your mind a mental model of the processes which are taking place.

To begin with, we shall be looking at memory and the formats in which programs and data are stored. We shall then go on to see how data is taken from memory and processed by the CPU during the execution of a typical machine code instruction.

Initially, we shall not be too concerned about the language we use for the instruction, nor about the precise way in which data is specified, or how we select the method by which it is sent to and received back from the CPU. Instead we shall concentrate on the general pattern of events; how the different elements of the system relate to each other and how the data is used to represent meaningful functions.

#### Memory, Addresses and Data

Firstly, we need to construct for ourselves a mental model of a computer's memory. A clear understanding of memory structure is essential to the understanding of how assembly language works and you will need to relate much of what you read in the following chapters to the events which you visualize taking place within the memory space.

We shall start by looking at the meanings of the terms *addresses* and *bytes*, because these are two of the main concepts from which our memory model will be constructed.

Memory consists of a sequence of separate, numbered locations in which items of information such as data and programs can be stored. There is no need for you to understand the actual physical structure of memory, as it exists on a chip. It is more helpful to imagine it simply as a series of numbered boxes into which programs and data can be placed. These can be pictured as a horizontal or vertical series of numbered pigeon holes, or, sometimes, as a two-dimensional matrix, whichever is most convenient for understanding a particular process.

Because memory locations are sequentially numbered, the number corresponding to each location is termed an *address*, in the same way that houses in a street are given address numbers. Figure 1.1 shows a number of possible representations of memory addresses.

| DDRESS 30000         |               |               |               |

|----------------------|---------------|---------------|---------------|

| (a)<br>ADDRESS 30000 | ADDRESS 30001 | ADDRESS 30002 | ADDRESS 30003 |

|                      | (             | b)            |               |

| ADDRESS 30000        |               | ]             |               |

| ADDRESS 30001        |               | (c)           |               |

| NDDRESS 30002        | Jacob menine  | ]             |               |

| ADDRESS 30000        |               |               | ]             |

| ADDRESS 30002        |               |               | (d)           |

| HDDRESS 30004        |               |               |               |

- FIGURE 1-1. a) Single address

- b) Row of consecutive addresses

- c) Column of consecutive addresses

- d) Two-dimensional array

The use of address numbers in assembly language is of vital importance because it is only by keeping track of addresses that the computers's CPU can find its way through a program. Just as in BASIC, where programs are given line numbers to indicate to the computer the order in which commands are executed, the CPU always needs to be aware of the address of the next machine code instruction which is to be executed. In the case of conditional branching operations, where execution is redirected to a subroutine for example, the CPU needs to keep a record of the address from which the branch was made so that it can return and pick up the sequence from where it left off. The programmer also needs to be aware of the address numbers of certain memory locations because particular items of data may be stored in specific places and there has to be a precise method of locating each one.

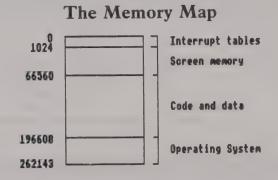

In our imaginary model, we shall assume that we are working with a computer which has a memory capacity of 256K. Since 1K of memory actually equals 1024 memory addresses, 256K therefore represents 262 144 addresses. We shall assume that address numbers 0 to 1023 are allocated to various items of data required by the computer's operating system (OS). Addresses 1024 to 66559 are allocated to the display memory, in which images which are visible on the VDU screen are stored. Addresses 66560 to 196607 are a free user area into which our own programs and data are loaded and addresses 196608 to 262143 are occupied by the computer's operating system. This model is greatly simplified but it illustrates the main areas into which memory is typically divided.

When we speak of 'addressing' a memory location, we mean that the CPU can have its attention directed to any one of the address locations in the system, including those in both RAM and ROM. In the case of the 68000, up to 16 million memory locations can be addressed, although in practice, many micros have much less memory available than this – usually 128 to 512K in total. The CPU can 'read' data from both RAM and ROM – that is, it can identify the contents of any addresses in these areas – and it can 'write' to any of the addresses in RAM – that is, it can insert fresh data into any of the RAM addresses.

#### **Bytes**

Data of any kind which is stored in a single memory address is recorded as a binary *byte*, representing an integer number between 0 and 255.

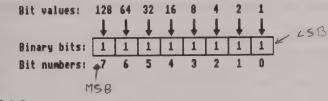

Each of the eight digits in a binary byte is termed a *bit* and a group of four bits, not surprisingly, is called a *nibble*. Each bit in a binary byte can represent either 0, in which case it has no value, or 1, in which case its value depends on its position within the byte. If the bit on the extreme right of the byte (the LSB or least significant bit) is set to 1 it has the value 1. A set bit in the second position has the value 2, the next 4, and so on through 8, 16, 32, 64 and finally 128, the value of the most significant bit (MSB).

FIGURE 1-2.

The total value of a byte is found by adding the individual values of its set bits, as follows:

11001001 = 201 decimal (128+64+8+1)

The reason why numbers are stored in this integer binary form is that in a computer, each set bit in a binary number, that is, each bit which is a 1 rather than 0, constitutes a signal which is translated within the machine as a voltage. It is only in the form of an electric current that binary numbers can physically be transported around the system from one component to another; for example between the processor and a memory chip.

The consequence of using integer binary storage is that individual memory addresses can never contain data representing 'real' (floating point) numbers as such. The decimal number 3.76 might be represented by the value '3' in one address and the value '76' in the following address, although there are a number of other ways in which real numbers may be stored.

In Part 1 of this book we shall be using the binary representation of numbers extensively because in this format it is much easier to follow exactly what is happening to data when certain assembly language instructions are executed. It is a good idea to get into the habit of imagining your data in binary form in the earlier stages because it helps considerably in understanding some of the more complex concepts involved. In Part 2 we shall go on to use hexadecimal numbering, which will allow us to represent numbers in a much shorter form without straying too far from the clarity which binary numbers allow.

It is important to remember that *all* data contained in memory is in binary numeric form, including program instructions and textual data. If we were to list the data bytes contained in a block of addresses it would be difficult to distinguish between those values which represent program instructions and those which represent program data. How, then, is the processor able to distinguish between them?

The answer is that every assembly language instruction has a unique numeric code of its own, consisting of between two to ten bytes and, providing the processor begins by reading a program from the very first instruction byte, it is capable of decoding and distinguishing the form and function of every byte thereafter. However, if the program begins execution at the wrong address, or if an instruction has been coded incorrectly, the processor is no longer able to make sense of any of the code and the result is usually a complete system crash.

The following diagram shows the binary code of a 68000 addition command, ADDQ #1, D2 which adds the value 1 to another operand which is contained in a temporary storage location called a register: in this case register 'D2'.

| ADDRESS 30800 |   |   |   | . 1 | DD | RE | \$\$ | 3 | 100 | 01 |   |   |   |   |

|---------------|---|---|---|-----|----|----|------|---|-----|----|---|---|---|---|

| 01            | 0 | 1 | 0 | 0   | 1  | 0  | 0    | 1 | 0   | 0  | 0 | 0 | 1 | 0 |

#### FIGURE 1-3.

This is a two-byte instruction consisting of the byte values 82 and 66; a code which uniquely represents the assembly language mnemonic ADDQ #1,D2. This object code consists of a 4-bit code representing 'ADDQ' (0101), a 3-bit code representing the number to be added (001), a zero, which is an additional part of the 'ADDQ' code, a 2-bit code specifying the (two-byte) size of the operation (01), a 3-bit code indicating the addressing mode of the instruction (000) and a 3-bit code indicating register 'D2' (010). Together these constitute two binary bytes: 01010010 (82) and 01000010 (66). The instruction ADDQ #1,D2 is what you would actually write in your program and the values 82 and 66 are the object codes which are assembled for execution.

The number of bytes required for each possible variation of a particular instruction is fixed and the CPU therefore knows that the next byte it comes across will be the beginning of the following instruction.

Code representing data, such as variables and arrays, is stored in completely different areas of memory from program code and under normal circumstances the processor will never attempt to execute it by mistake.

#### Words and Long Words

Although a single byte has a maximum value of 255, you will obviously want to work with numbers which are much larger than this. In fact, the binary byte is only a basic unit of data; you can store binary numbers using several bytes if you wish. For example, a 2-byte integer represents a binary number of 16 binary digits, giving a decimal range of 0 to 65 535. A 16-bit value is termed a word and a 32-bit (4-byte) value is termed a long word, which can represent a decimal value between 0 and 16 777 215. When the 68000 is referred to as a '16-bit' microprocessor, this does not mean that you are limited to 16-bit numbers; it is simply a reference to the way in which the processor deals with numbers internally; it can 'read' or 'write' up to two bytes at a time, which does not actually affect the size of data which the programmer can deal with. A '32-bit' or a '64-bit' computer would be faster - which would make it more suitable for calculating a large prime number, predicting the world's weather or problems of a similar magnitude.

Data is stored in memory with the higher (most significant or 'hi') part of a binary value stored first, followed by the lower (least significant or 'lo') part. A single byte would, of course, be stored on its own in a single address. A two-byte (word) value, such as 36829, would be expressed in binary as

1000111111011101

and would be stored in memory as follows:

| ADDRESS 71712 | ADDRESS 71713  |

|---------------|----------------|

| 10001111      | 11011101       |

| 143           |                |

| HI BYTE       | 221<br>Lo byte |

FIGURE 1-4.

The decimal value is found by multiplying the hi byte by 256 and adding the lo byte  $(143 \star 256) + 221 = 36829$

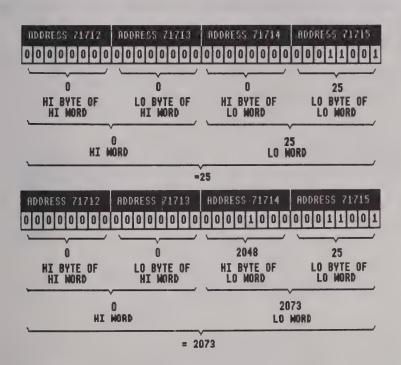

A 4-byte (long word) value, for example 131097, is expressed in binary, as

00000000 00000010 0000000 00011001 0 2 0 25

and would be stored in memory as follows:

| ADDRESS 71712 | ADDRESS 71713 | ADDRESS 71714 | ADDRESS 71715<br>00011001 |

|---------------|---------------|---------------|---------------------------|

| 0             | 2             | 0             | 25                        |

| HI BYTE OF    | LO BYTE OF    | HI BYTE OF    | LO BYTE OF                |

| HI WORD       | HI NORD       | LO WORD       | LO WORD                   |

| 131           |               | Z'            | 5                         |

| HI W          |               | LO N          | ORD                       |

= 131097

FIGURE 1-5.

In this case the decimal value is found by multiplying the hi word by 65536 and then adding the lo word: (2 \* 65536) + 25 = 131097.

Note that although byte and word values consist of 8 and 16 bits respectively, there are occasions when they need to be stored in longer binary form, such as 32 bits. In these cases the values can simply be extended with zero bytes and stored as if they were 32 bit numbers, e.g.:

FIGURE 1-6.

Similarly, single byte values can be stored as words:

|         | ADDRESS 71715 |

|---------|---------------|

| 0       | 25            |

| HI BYTE | LO BYTE       |

|         | -25           |

FIGURE 1-7.

It is important to note that all word and long word sized data items must start at an even numbered address, otherwise the system will signal an error condition. Byte data may be stored and accessed at both even and odd numbered addresses.

Here is a list of some of the different types of data which may be stored in memory addresses:

- 1 instruction codes: stored as 1-5 words

- 2 byte data: stored as 1 byte

- 3 word data: stored as 2 bytes

- 4 long word data: stored as 4 bytes

Before going on to look at how programs are organized in memory, we shall first look at how memory is typically arranged, so that we can imagine our program data in context.

FIGURE 1-8. Memory map.

In this simplified map of a computer's memory, you can see clearly how the space allocated to data is divided into different sections. On different computers the addresses of these divisions will vary and other specialized memory areas will be reserved for special data and functions. In this model for example, there is no area reserved for a BASIC language interpreter, although many computers may incorporate this. Most machine manuals will include a memory map diagram similar to this to show you how memory space is allocated. The first section, from addresses 0 to 1023 is reserved for special tables and other data used by the operating system. The second section, from 1024 to 66559 is reserved for the VDU display. Any data placed in one of these display memory locations will appear as an image on the screen. If a computer has colour capabilities, the data specifying the background and foreground colours of an image will also occupy this section.

The display area is best illustrated as a two dimensional array of memory addresses, with each row corresponding to the full width of the screen and the columns representing the vertical height of the screen. In this diagram, only the addresses corresponding to the top left hand corner of the screen are illustrated:

| ADDRESS 1 | 024    |  |

|-----------|--------|--|

| ADDRESS ] | 157    |  |

| IDBRESS 1 | (7BU   |  |

| ROORIS! 1 | 1400 · |  |

| RDDRESS 1 | 536    |  |

FIGURE 1-9. Display memory corresponding to top left-hand corner of screen.

In our imaginary computer the 'display' section is fixed and so the precise location of any point on the display screen can easily be calculated. On some computers, although the actual length of the display section remains constant, its position within memory may change constantly.

The 'code and data' section is the area which is reserved for programs and their associated data, whether they be written in BASIC, assembly language or any other language.

In BASIC programs the data area is used to store variables and arrays and their formats are organized by the BASIC interpreter. In assembly language, variables, arrays and other types of data are stored in reserved blocks of memory created by the programmer rather than by resident software and therefore it is necessary to be able to identify the locations of the addresses in this area in order to store and retrieve this information. The operating system consists of sets of routines designed for structuring the way in which the system functions and includes control mechanisms for communicating with disc drives, error handling, input and output operations, keyboard and VDU communications and other administrative tasks. Customized extensions to the operating system may include complex arithmetic and graphics functions and other routines which, like most of the operating system, are accessible from user programs.

#### **Program and Data Storage**

We shall now look at a simple model of how a typical assembly language program and its data is stored in memory. We shall assume that our program occupies addresses 71680 to 71707. Henceforth the term 'address' will be used interchangeably to refer both to the number of a particular location and the physical location itself. The term 'content' will be used to refer to the data contained in an address, irrespective of whether it is code which forms part of a program instruction or whether it is data representing a character or a numeric value.

Thus our program code occupies 27 addresses and the contents of the first six of these can be pictured as follows.

| ADDRESS 71680 | 116 | Instruction |

|---------------|-----|-------------|

| ADDRESS 71681 | 0   | Data        |

| ADDRESS 71682 | 24  | Instruction |

| ADDRESS 71683 | 58  | Instruction |

| ADDRESS 71684 | 0   | Data        |

| ADDRESS 71685 | 44  | Data        |

FIGURE 1-10. Program code.

The instruction codes each occupy a varying number of addresses and in some cases are followed by addresses containing data. These data items are treated as being part of an instruction and may represent either constant data values or data representing the address of another location. The variable data for our program, stored in the 'data' section of memory, is 5 bytes in length and occupies, say, addresses 71712 to 71716.

| ADDRESS 71712 | 24 |

|---------------|----|

| ADDRESS 71713 | 21 |

| ADDRESS 71714 | 28 |

| BDDRESS 71745 | 28 |

| ADDRESS 71716 | 31 |

FIGURE 1-11. Program data.

You will notice that the 'program code' section also contains data as well as instruction codes, and you may be wondering why this data is different from the data in the 'data' section. The reason is that there is a distinction between 'immediate' data, which relates to a particular instruction, and array and variable data stored in the data area. For example, in the BASIC instruction LET A=8\*X the value '8' is stored along with the BASIC instruction itself, whilst the value of the variable 'X' is fetched from the 'data' section of memory during execution. In other words, the '8' is always 8 and is part of the program command, whilst X may be one of a number of possible values, and would be stored in the variables section of memory.

Now consider what happens when our program is executed. It may be one which has been designed, for example, to add the value 48 to each of the contents of the addresses in the 'data' section and to print the results to the screen. It should be easy to follow the general sequence of events which take place.

Two of the instructions in the program area instruct the computer to take the constant 48 (termed the source operand) and add it to the contents of the first address in the data area (termed the destination operand). The next instruction then places the ASCII character corresponding to the sum in some of the addresses in the display section. Figure 1.12 illustrates part of the processes involved.

The ASCII characters in a computer are a standard set of characters which include all alphabetic letters, numerals, punctuation marks and essential control codes such as line feed, carriage return and so on. The binary codes for all these characters are always positive numbers in the range 0 to 127. The remaining ASCII codes, 128 to 255, are assigned by different computer manufacturers to various other functions and are not standardized.

| ADDRESS n                                                                                                                         | 18                                             |                                                                              |                                                                                        |     |    |             |    |             |   |  |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|----|-------------|----|-------------|---|--|

| ADDRESS n+1                                                                                                                       | 50                                             |                                                                              | Get an item of data<br>from the first address<br>in the data section<br>(the value 24) |     |    |             |    |             |   |  |

| ADDRESS Nº 2                                                                                                                      | 32                                             | in the dat                                                                   |                                                                                        |     |    |             |    |             |   |  |

| RDDRESS n+3                                                                                                                       | 0                                              | Cite value                                                                   | 24)                                                                                    |     |    |             |    |             |   |  |

| ADDRESS n+4                                                                                                                       | 210                                            | 71                                                                           |                                                                                        |     |    |             |    |             |   |  |

| ADDRESS A+5                                                                                                                       | 58                                             | Add 48 to                                                                    | it (                                                                                   | 484 | +2 | <b>(</b> =) | 72 | >           |   |  |

| ADDRESS ###                                                                                                                       | 0                                              |                                                                              |                                                                                        |     |    |             |    |             |   |  |

| HDDRESS ###                                                                                                                       | 31                                             | 7                                                                            |                                                                                        |     |    |             |    |             |   |  |

| ADDRESS AT#                                                                                                                       | 114                                            | ]]                                                                           |                                                                                        |     |    | _           |    |             |   |  |

| annancer in                                                                                                                       | OFF                                            | Call a subroutine                                                            |                                                                                        |     |    |             |    |             |   |  |

| HDDRESS n+9                                                                                                                       | 255                                            | to print R                                                                   | SUIT                                                                                   |     |    |             | _  | 1           |   |  |

| RDDRESS n+10                                                                                                                      | <u> </u>                                       | code 72                                                                      | SUIT                                                                                   |     |    |             |    |             |   |  |

| RODRESS n+10                                                                                                                      | 118                                            | ADDRESS 102                                                                  |                                                                                        |     |    |             |    |             | Т |  |

| RODRESS n+10                                                                                                                      | gets the                                       | J I                                                                          |                                                                                        | 1   |    |             |    | 1           | Ŧ |  |

| RODRESS m+10<br>Display subroutine<br>address of the scree<br>the address of the<br>binary pattern for                            | gets the<br>en cursor,<br>stored<br>RSCII code | ADDRESS: 1024                                                                |                                                                                        | 1   |    |             |    | 1           |   |  |

| RODRESS n+10                                                                                                                      | gets the<br>en cursor,<br>stored<br>RSCII code | ADDRESS 1024<br>BDDRESS 115                                                  |                                                                                        | -   | 1  |             | 1  |             |   |  |

| RODRESS mild<br>Display subroutine<br>address of the scree<br>the address of the i<br>binary pattern for i<br>2 (character W) and | gets the<br>en cursor,<br>stored<br>RSCII code | ADDRESS 1024<br>ADDRESS 115<br>ADDRESS 115                                   |                                                                                        | 1   | 1  | 1           | 1  | 1           |   |  |

| RODRESS mild<br>Display subroutine<br>address of the scree<br>the address of the i<br>binary pattern for i<br>2 (character W) and | gets the<br>en cursor,<br>stored<br>RSCII code | ADDRESS 1024<br>BDDRESS 1152<br>BDDRESS 1280<br>ADDRESS 1280<br>ADDRESS 1408 |                                                                                        | 1   |    | 1           | 1  | 1<br>1      |   |  |

| RODRESS mild<br>Display subroutine<br>address of the scree<br>the address of the i<br>binary pattern for i<br>2 (character W) and | gets the<br>en cursor,<br>stored<br>RSCII code | ADDRESS 1024<br>BDDRESS 1152<br>RDDRESS 1280<br>ADDRESS 1408<br>BDDRESS 1536 |                                                                                        | 1   |    |             |    | 1<br>1<br>1 |   |  |

#### FIGURE 1-12.

In practice, the operation involves the *movement* and the *processing* of data in which all the relevant items, including the instruction and the data codes, are physically copied into the CPU, processed, and the resulting data transported to memory addresses in the display area.

The technical aspects of these operations need not necessarily be understood in detail by the programmer, since the CPU controls the sequence of events automatically.

When the first numbers have been added together and the corresponding ASCII character printed to the screen, the process can be repeated with the second item of data by looping back and repeating the first instruction. This process may then be repeated until all five additions have been completed and the characters printed to the screen.

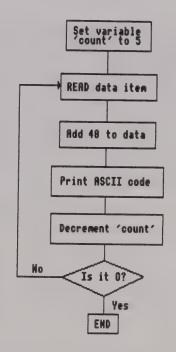

The following example shows how the same operation might be performed in BASIC:

10 FOR count = 5 to 1 STEP -1 20 READ V 30 PRINT CHR\$(48 + V) 40 NEXT count 50 DATA 24,21,28,28,31

This produces the values 72, 69, 76, 76 and 79, for which the corresponding printed ASCII characters are 'HELLO'.

The assembly language and BASIC processes have a number of similarities:

- 1 The instructions in both programs are executed sequentially, except for the loop sequence, which allows a section of the program - to be repeated.

- 2 Both store their variable data separately and call up each item of data when it is needed.

- 3 Both require their instruction codes and program data to be sent to the CPU for processing during execution.

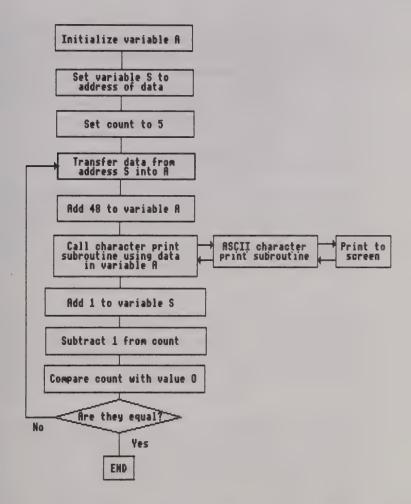

If we look at a flowchart for each version we shall also see some very important differences in the way in which the operations are carried out:

FIGURE 1-13. Flow chart for BASIC version.

The first main difference is that the assembly language version is much longer, breaking down the individual steps in the operation to smaller, closely defined units. The BASIC program operates in almost the same way when it is executed but the individual steps are handled entirely by the machine's BASIC interpreter, leaving the programmer to structure the program using easily understood broad concepts such as the FOR..NEXT loop and the READ..DATA functions. Hence, the BASIC flowchart illustrates the flow of BASIC language mechanisms while the assembly language flowchart illustrates the *actual* flow of events between memory and the CPU.

The second difference is that although the BASIC version implies that data should be moved around in memory, the physical movement of the data is not specified. Although items of data are added and then transferred to the screen, the program itself does not concern itself with the precise locations of the data or where it should be moved to.

The assembly language version on the other hand, is very specific about where the different elements of the program are located and where they should be moved to. Thus an assembly language program consists not only of instructions specifying standard operations, such as addition and subtraction, but of instructions designed to locate and control the movement of different categories of data throughout the system.

Unfortunately, the range of operations which the CPU can perform is very limited and therefore it is not possible, for example, to write an instruction which transfers a numeric value into it and requests its cosine or logarithmic value as you would use COS or LOG in BASIC. In fact it deals entirely with integer values and is only capable of adding, subtracting and performing logical operations on them such as AND and OR. Although the CPU cannot handle multiplication and division directly, the 68000 system incorporates instructions which can perform these operations and therefore this is not a problem.

Should you require a more complex computation such as the cosine or logarithm of a number, then it is necessary to break down such an operation in terms of simple arithmetic and logical steps which the CPU can perform. There is no need to be deterred by this because with many computers it is possible to take a short cut by using ready made mathematical functions which are already programmed into the operating system. You can simply regard such functions as assembly language subroutines and call them up from within your own program. In some cases a system will incorporate an arithmetic co-processor which is designed to handle transcendental functions and floating point numbers. These incorporate their own instruction set and allow you to specify the operands involved and the mathematical function required.

#### Assemblers

Assembly language, like any other computer language, consists of a set of instructions, representing specific program operations, and a syntax, which specifies the format in which instructions may be written. The reason why it is called assembly language is that it is designed to be used with an *assembler program*, which interprets the instruction mnemonics written by the programmer (the *source code*) and converts them into a set of numbers which can be interpreted and executed by the computer. The resulting numbers are called the *object code* or *machine code*.

A program which is written in assembly language cannot be run in the way that a BASIC program can; only the object code can be executed, and it is this code which is assembled and saved to tape or disc prior to being loaded and executed. The resulting machine code program is simply a list of numbers which represent particular instructions and some which represent data, as described previously.

When a BASIC program is run the instructions are *compiled* (translated) from BASIC to machine code at the time of execution. If we were to use a *disassembler* (i.e. a program for converting machine code back into assembly language) to examine the contents of a machine code program we would be given a listing which looked something like the following:

| Address<br>(hexadecimal) | <i>Object Code</i><br>( <i>hexadecimal</i> ) | 68000 Instruction<br>Mnemonics |

|--------------------------|----------------------------------------------|--------------------------------|

| 29CE8                    | 7200                                         | MOVEQ #00, D1                  |

| 29CEA                    | 7602                                         | MOVEQ #02, D3                  |

| 29CEC                    | 41FA0038                                     | LEA 38(PC)!29D26, AD           |

| 29CF0                    | 7001                                         | MOVEQ #01, DO                  |

| 29CF2                    | 4E42                                         | TRAP #2                        |

| 29CF4                    | 7400                                         | MOVEQ #00, D2                  |

| 29CF6                    | 183A002C                                     | MOVE.B 2C(PC)!29D24, D4        |

| 29CFA | 45FA0022 | LEA 22(PC)!29D1E, A2   |

|-------|----------|------------------------|

| 29CFE | 12322000 | MOVE.B 00(A2,D2.L), D1 |

| 29002 | D23A001F | ADD.B 1F(PC)!29D23, D1 |

You will see that we are given three different types of information. In the left hand column we have a list of addresses (in hexadecimal format) which represent the locations in which the machine code program is stored in memory. The right hand column contains the assembly language instruction mnemonics for the program and the centre column contains the hexadecimal machine code version of the assembly listing on the right. The machine code is divided into different groups of bytes, with each individual byte (2 hexadecimal digits) representing the contents of a single memory address.

The first instruction, MOVEQ #00,01 is translated into two bytes of object code, occupying addresses 29CE8 and 29CE9<sub>H</sub>. The second instruction also occupies two bytes while the third instruction, LEA 38(PC)!29D26, A0 consists of 4 bytes, and occupies addresses 29CEC to  $29CEF_{H}$ .

The machine code program would be executed sequentially, starting with the first number of the code of the first instruction and continuing through each memory byte until a final instruction is reached. In between there may be program loops, subroutine calls and conditional jumps, just as there are in BASIC programs.

The program is initiated either by an auto start mechanism, as soon as it has been loaded into memory, or by calling it with a high level language instruction, for example from within a BASIC program or from the operating system. Alternatively, a program may be a *subroutine* which is called from within some other machine code program.

In Chapter 8 we shall be looking at assembler programs in more detail, showing how the translation from assembly language to object code is organized.

## Chapter 2

### **Registers and Addressing Modes**

#### **Sources and Destinations**

When an item of data is accessed and transferred from one location to another, for example when data in one location is added to another item of data, the the first item is termed the *source* operand and the second item, the *destination* operand. The terms source and destination are used extensively in assembly language to distinguish the status of the operands involved in an operation. As we shall see later, the possible source and destination locations for operands involved in different operations may be subject to entirely different rules. In the case of the addition instruction in the previous chapter (ADDQ#1,D2), the source operand, 1, is an immediate numeric constant, while the destination operand is located in a register. The register itself is the destination location, the contents of the register being the actual destination operand. When the two operands have been added, the result is automatically stored in the location which previously held the destination operand.

#### Registers

An operand which is being addressed by an assembly language instruction will be in one of two places; either in a memory location (in either the code or data sections) or in a *register*.

Registers are identified by alphabetical letters, like BASIC variables, and are literally temporary memory locations which are situated in the CPU rather than in RAM or ROM. A register may be treated in much the same way as any other memory location in that data may be loaded into one or moved out of one into another location and the contents of registers may have arithmetic operations performed on them. Some are also used as temporary variables for holding the codes of memory addresses.

In the 68000 there are two main types of user registers; *data registers* (D0, D1, D2, D3, D4, D5, D6 and D7) and the *address registers* (A0, A1, A2, A3, A4, A5 and A6), each of which hold up to four bytes of data. The address registers are normally used for holding the addresses of memory locations.

#### **Data Registers**

Data registers are 32 bits in length and are capable of holding data of byte, word and long-word lengths. You can imagine them simply as labelled boxes divided into four byte-sized partitions which can be loaded with binary values. The least significant byte of a value occupies the right hand partition and the most significant byte occupies the left, corresponding to the way in which you would normally format a binary number.

As an example of the use of a general data register, suppose that you had a program in which repeated calculations were being performed on a set of figures and you wish to add up the totals. Just as you might use a variable in BASIC to accumulate the total, you could use a data register such as D2 in assembly language. As with a BASIC variable, the value contained in a data register can be used in subsequent program instructions.

FIGURE 2-1.

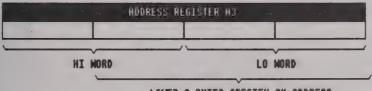

## **Address Registers**

An address register is also 32 bits in length and, like a data register, is used as a source or destination for operands. However, whereas the purpose of a data register is simply to hold data which is being used in a program, an address register is used specifically to hold address numbers. Although an address register can actually hold a 32-bit value, only the least significant 24 bits (bits 0 to 23) of a value are used to specify an address, hence the maximum restriction in a 68000 based computer to 16 777 216 bytes (16 megabytes) of physical memory. Note that a 68008-based computer is restricted to a maximum of 1 megabyte, since only the lower 20 bits of an address register can be used to specify an address.

LOWER 3 BYTES SPECIFY AN ADDRESS

FIGURE 2-2.

### **Additional Registers**

In addition to the address and data registers, the 68000 has a small number of other registers which are used for special purposes.

### **Program Counter**

The PC (program counter) register is a 32-bit register whose lower 24 bits always contain the address of the program instruction that is currently being executed and is automatically updated by the system as each instruction is processed. Whenever a program branches to a subroutine or jumps to another point in the code, the new address is automatically loaded into the PC register so that the processor knows from where in memory to fetch the next instruction. The address contained in the PC register can be altered by the programmer to redirect execution to a different point in the program, but this is

normally only done in special circumstances, for example if there is an occasion when you want to return from a specific subroutine to a point other than the normal return address. Under normal circumstances, you would only need to refer directly to the PC register if you wish to refer to an address which is a specified number of bytes relative to the current execution address.

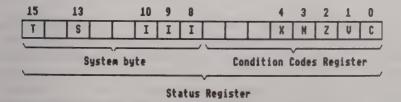

### **Status Register**

The status register (SR) is a 16-bit register which is used to hold a number of bit-sized 'flags' which indicate the current status of the system. It is used to determine, for example, whether a computed value is positive or negative, whether it is less than, equal to or greater than some other value or whether it involves an arithmetic 'carry' or 'borrow'. The main functions of the status register are described in detail in the following chapter.

#### **Stack Pointer**

A special area of memory, termed the *stack*, is reserved for the storage of temporary data and variables. The current location of the 'top' of the stack; the point at which fresh data may be stored or old data removed, is at the address whose value is contained in address register A7. This register is therefore referred to as the *stack pointer* (SP), since it 'points' to the current stack top.

### **Addressing Modes**

The available methods by which data may be accessed and moved around between memory locations, registers and the processor itself are termed addressing modes and these are clearly defined. It is not necessary to think too consciously about which mode to use in a particular situation, any more than it is necessary to think about the rules of grammar whenever you wish to speak. If you know where your data is and what you want to do with it then the appropriate addressing mode will come to mind automatically in most cases. However, it is useful to be aware of what is possible and what is not and the following section describes the formal structure of these modes. In this section we shall be starting to use some actual assembly language instructions, beginning with the MOVE instruction, which is used to copy operands from a source to a destination, and the ADD and SUB instructions, which add and subtract operands. There are two main categories of addressing modes: *memory* addressing, in which operands contained in memory are addressed, and *register addressing*, in which operands located in registers are addressed. Although registers do not actually have address numbers of their own to identify their location, the term 'addressing' nevertheless includes register as well as memory references.

## **Implicit Addressing**

Certain assembly language instructions involve the use of particular registers without explicitly stating which registers are to be used. In all cases, these instructions use one or more registers for the same reasons as you would choose to use one yourself: to store, retrieve, move, process or modify data. In these cases however, the particular register used is chosen for a specific purpose and therefore there is no need for the programmer to indicate which one is required. For this reason, this addressing mode is termed *implicit*, for the register to be used is implicit in the instruction itself. Such instructions include, for example, RTS (return from subroutine) which always implies the contents of the PC register. Some instructions are not only implicit, in that they imply the contents of SP and/or PC, but also involve the use of other addressing modes.

### **Register Direct Addressing**

This addressing mode is used for operations performed on data contained in registers. For example, the contents of two registers may be added together or the contents of one may be transferred to another. In BASIC, equivalent instructions would include LET A=B or LET A=A+B.

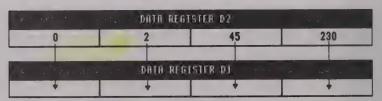

In the first of these examples you will notice that the MOVE instruction has a '.L' after it, whilst in the second, it has a '.W'. The reason for this is that the first example is a 'long-word' operation, in which all four bytes of one register are copied into the other. In the second example, which is a 'word' operation, only the least significant word of a register is involved, leaving the most significant word of each register unchanged. This distinction has nothing to do with the fact that one is a MOVE operation and the other an ADD operation – we

OPERATION: MOVE.L D2,D1 (copy the entire contents of data register D2 into data register D1)

| and the second               | DATA REG | ISTER D2 |     |

|------------------------------|----------|----------|-----|

| 0                            | 2        | 45       | 230 |

| en tra Alexandria, en esta a | DATA REG | ISTER D1 |     |

|                              |          | +        | +   |

OPERATION: ADD.N D2,D1 (add the low order word of register D2 to register D1)

### FIGURE 2-4.

could just as easily have specified the instructions MOVE.W D2,D1 and ADD.L D2,D1; the '.W' and the '.L' being the parts of the instructions which determine the size of the operands involved in the operations.

In both cases we could alternatively have used the instruction suffix '.B', signifying that only the least significant byte of the register contents be involved. If there is no '.B', '.W' or '.L' suffix after such an instruction, it is normally assumed by default that '.W' is intended although there are exceptions to this rule.

The two registers involved can both be data registers or one of them can be an address register. In the instruction MOVE A2, D1 for example, the source operand is specified by address register direct addressing and the destination is specified by data register direct addressing.

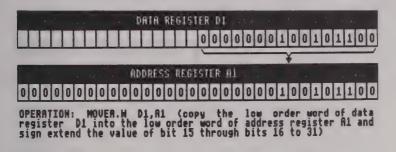

The same type of operation performed using an address register as a *destination* is slightly different. In this case, only two sizes of data may be used in an operation – word and long-word. Therefore, the '.B'

FIGURE 2-3.

suffix cannot be used. Some instructions indicate the use of an adress register destination by the addition of an 'A' to the instruction mnemonic, such a MOVEA and ADDA. The other important difference is that, if an address register is being used as the destination register for an operation, *all four bytes are affected*, unlike a data register where the unused bytes remain unaffected. If we were to transfer a word of data, say the value 300 (binary 0000000100101100) from register D1 to register A1, the most significant word of A1 would automatically be *sign-extended* to a full 32 bits – in other words, the highest bit of the least significant word, bit 15, would be copied into bits 16 to 31 of A1, as follows:

### FIGURE 2-5.

The implications of this are very important because it affects the way in which a memory address is specified. If we load a 4-byte (long-word) address into an address register, then the address which it represents will be the one specified by the least significant 24 bits of the register, as described above.

However, if we load a word value into an address register, the remaining two bytes of the register, the Hi word, will carry the *sign-extension* of the value and part of this will be incorporated in the 24-bit address specification. How does this affect the value of the address which we wish to specify?

There are two possible alternatives. If the value loaded into the address register is between 0 and 32767 decimal, the binary representation in the register will be as follows:

011111111111111 binary = 32767 decimal which, after being sign-extended in the address register would be the same:

```

0000000000000000111111111111111 binary

= 32767 decimal

```

So far so good. This address is the highest in the bottom 32K of memory and is exactly the address we specified when we loaded it into the address register; sign-extension left it unchanged.

However, the alternative possibility is that we load a word value between 32768 and 65535 decimal into the address register. The binary representation would be as follows:

100000000000000 binary = 32768 decimal

which, after being sign-extended in the address register would become (counting only the lower 24 bits):

```

11111111111111111000000000000000 binary

```

= 16 744 448 decimal

This address happens to be the first address of the *top 32K* of memory – not the address we originally specified. This is not a fault but an advantage. If we actually want to access a memory address in the top or bottom 32K of memory then we only need to use a word (in the range 0 to 32767 or 32768 to 65535) to specify the address, which is a saving in both time and space. Hence, a word-sized address is termed a *short* address.

If we want to access an address *anywhere* in memory, we use *long* addressing; that is, we load a long word address value into the address register which, since it will not be sign-extended, will produce exactly the address which we specify, up to a maximum of 24 bits. This principle applies to any addressing mode which makes use of an address register.

One final point to note about address register direct addressing is that in some cases where the destination of an operation is an address register, for example in ADDA (add address), SUBA (subtract address) and MOVEA (move address), the condition flags in the CCR register are not affected by the operation.

# **Absolute Addressing**

An absolute addressing operation is one in which an operand is identified by its actual memory address. In BASIC terms it is similar to the instructions LET A=PEEK(20000) or POKE 20000, A. In practice, the address is normally identified in the instruction by means of a user defined label rather than an actual number.

Direct addressing has *long* and *short* forms: a 'long' address, as already indicated, being specified by a 32-bit number and a 'short' address as a 16-bit number, sign-extended to 32 bits.

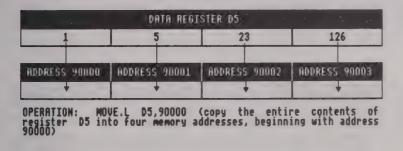

### FIGURE 2-6.

This is the long form of direct addressing. The address value is a 3-byte number and therefore the system automatically recognizes it as a literal address. The '.L' suffix has nothing to do with the address size; it performs its usual function of denoting the size of the data which is to be transferred.

| 1             | 5             | 23            | 126           |

|---------------|---------------|---------------|---------------|

| ADDRESS 20000 | RDDRESS 20001 | RDDRESS 20002 | ADDRESS 20003 |

| +             | +             | +             | +             |

FIGURE 2-7.

This is the short form of direct addressing. The address value is a 2-byte number, which is automatically sign-extended to 32 bits. Since the 2-byte number is within the range 0 and 32767, it falls into the bottom 32K of memory and, after sign-extension, it therefore remains unchanged. As in the previous example, the '.L' suffix indicates that four bytes are to be transferred.

### **Immediate addressing**

This is used for operations involving an immediate numeric constant. For example, a number may be transferred from or loaded into a register or, it may be added to or subtracted from a number which is already in a register. Equivalent BASIC instructions would be LET A=10 or LET A=A+10.

FIGURE 2-8.

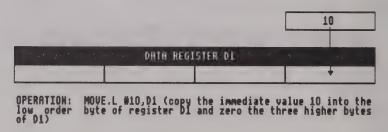

Note that here, the '.L' suffix has been used to indicate that D1 should contain a 32-bit binary representation of 10. This would normally be done if we wish to ensure that the unused bytes of a data register are zeroed. The '#' sign is used to indicate that the value is an immediate constant.

FIGURE 2-9.

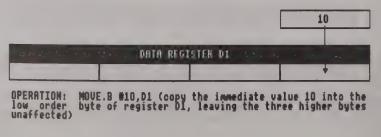

In this case the '.B' suffix has been used, specifying that the value 10 is only copied into the least significant byte of D1, leaving the rest unaffected.

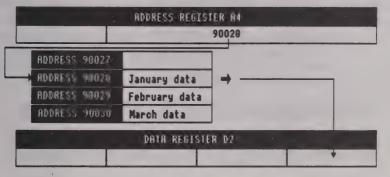

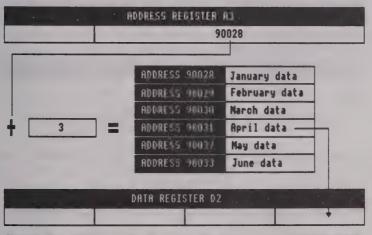

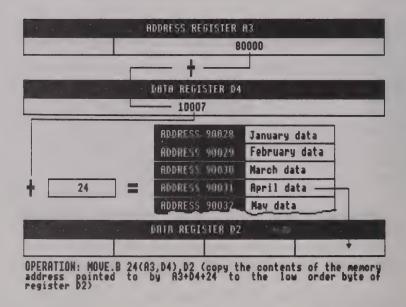

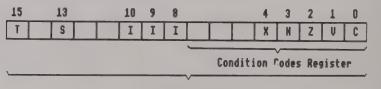

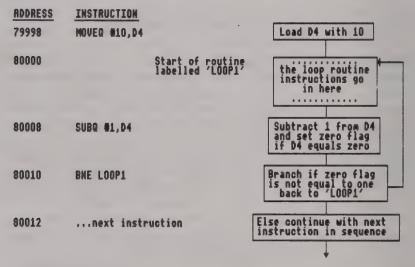

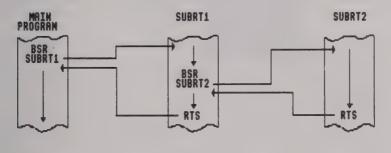

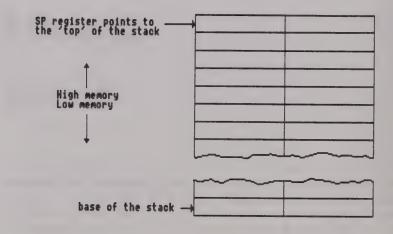

### **Immediate Quick Addressing**